- Japanese

- English

JavaScript is disabled.

Please enable JavaScript to watch this content.

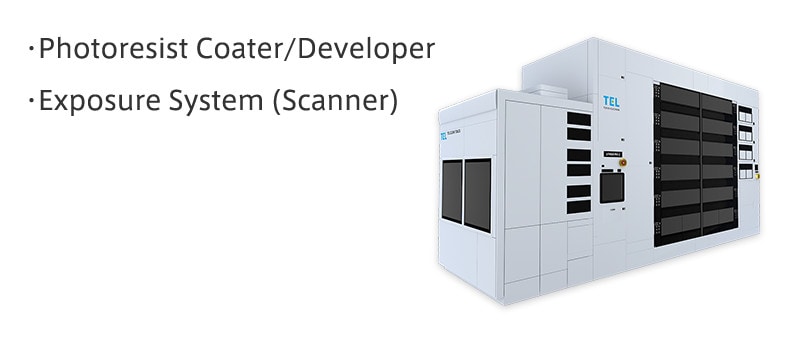

A gate dielectric film (oxide film) is deposited by thermal oxidation, followed by surface nitriding treatment. A gate electrode layer (polysilicon film) is then deposited by the CVD process.

The patterning process is implemented on the gate electrode layer to form the source and drain region.

The elements extracted by the ion implantation process (boron, arsenic, etc.) are doped into the source and drain region. The area covered by the residual oxide film is not doped. The doped impurities are spread uniformly in the trenches by means of high temperature anneal.

An oxide film is deposited through the CVD process to form an intermetal dielectric film, and the surface is polished and planarized.