#### Tokyo Electron IR Day

February 26, 2025

#### Forward Looking Statements

Disclaimer regarding forward-looking statements

Forward-looking statements with respect to TEL's business plan, prospects and other such information are based on information available at the time of publication. Actual performance and results may differ significantly from the business plan described here due to changes in various external and internal factors, including political and economic situation, semiconductor market conditions, intensification of sales competition, safety and product quality management, intellectual property-related matters and impacts from COVID-19.

#### Processing of numbers

For the amount listed, because fractions are rounded down, there may be the cases where the total for certain account titles does not correspond to the sum of the respective figures for account titles. Percentages are calculated using full amounts, before rounding.

#### Foreign exchange risk

In principle, export sales of Tokyo Electron's products is denominated in yen. Although some sales and expenses are denominated in foreign currencies, the impact of exchange rate fluctuations on profits is negligible, unless extreme fluctuations occur.

TFL

#### Agenda

| 1. Opening                                                                                       | 3:30pm - 3:35pm  |

|--------------------------------------------------------------------------------------------------|------------------|

| 2. Presentation                                                                                  | 3:35pm - 5:05pm  |

| <ul> <li>Market Outlook for Semiconductors and TEL's Growth Strategy</li> </ul>                  | Toshiki Kawai    |

| <ul> <li>Elevating Financial Position and Points for Future Growth</li> </ul>                    | Hiroshi Kawamoto |

| <ul> <li>Opportunities in Frontend Process Business and Activities in Digital x Green</li> </ul> | Jack Ishida      |

| <ul> <li>Activities in Coater/Developer and Cleaning System</li> </ul>                           | Yasuhiro Washio  |

| <ul> <li>Latest Technological Challenges and Activities in Etch</li> </ul>                       | Tetsuya Nishiara |

| <ul> <li>Business Strategy in Thin Film Deposition</li> </ul>                                    | Shigeki Nakatani |

| <ul> <li>Diverse Systems and Solutions</li> </ul>                                                | Kan Ishida       |

| <ul> <li>Technology Trends and Business Opportunities in Assembly Processes</li> </ul>           | Keiichi Akiyama  |

| <ul> <li>Product Strategy in Assembly Processes</li> </ul>                                       | Yohei Sato       |

| <short break=""></short>                                                                         |                  |

| 3. Q&A                                                                                           | 5:15pm - 6:00pm  |

Investor Relations / February 26, 2025

# TEL

## Market Outlook for Semiconductors and TEL's Growth Strategy

Tony Kawai President & CEO Tokyo Electron Limited

# **Digital & Green**

#### "Green by Digital" & "Green of Digital"

TEL 6

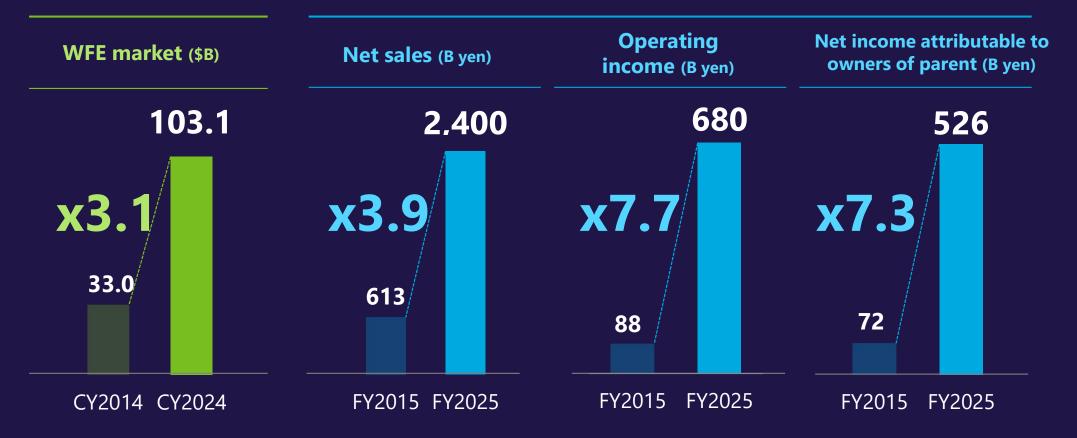

#### Comparison of FY2015 vs FY2025 Forecast

#### **Expected to significantly outperform market growth**

Source : TechInsights Manufacturing Analysis Inc. (VLSI)

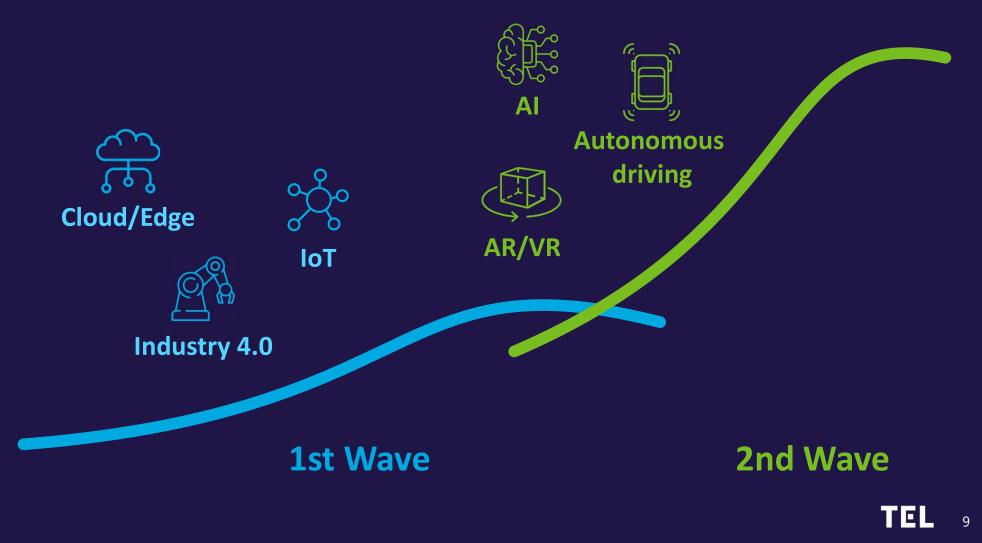

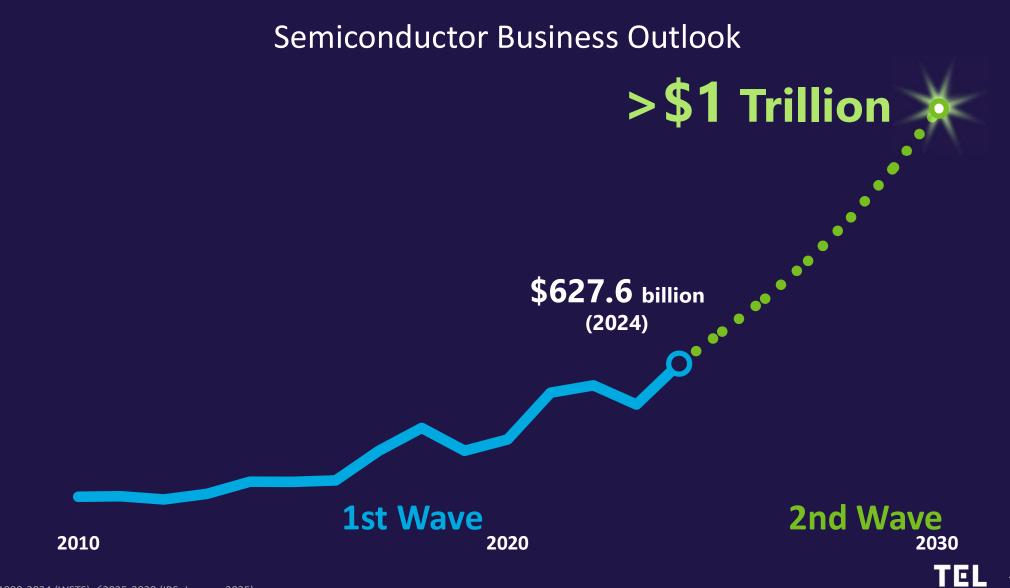

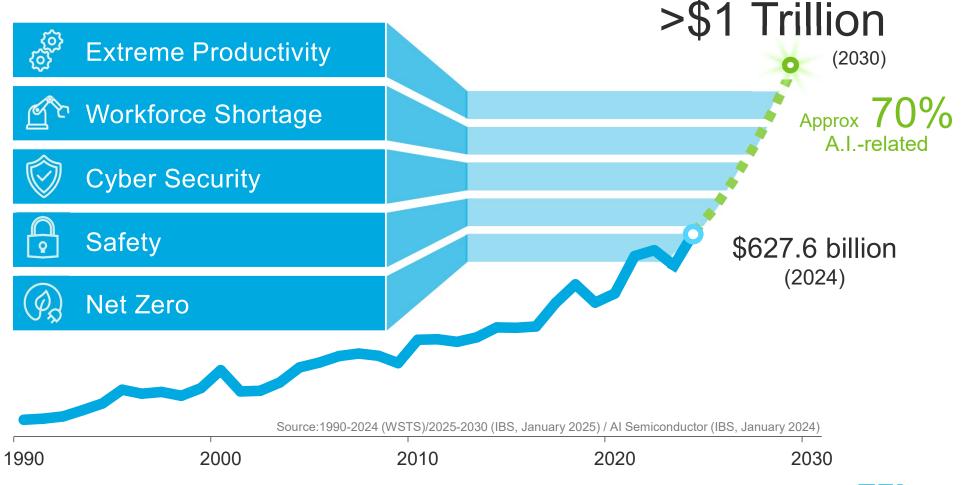

#### Semiconductor Business Outlook

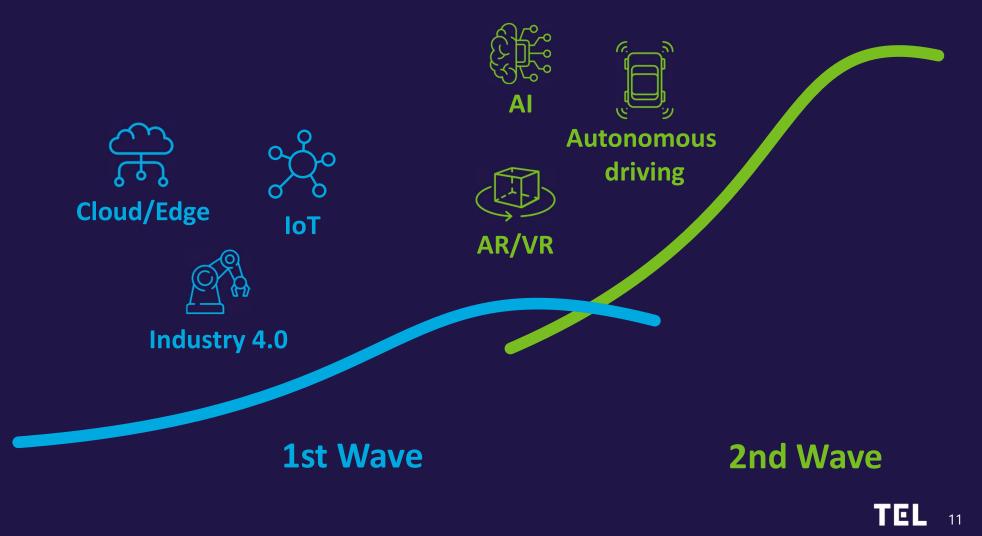

#### Semiconductor Business Outlook

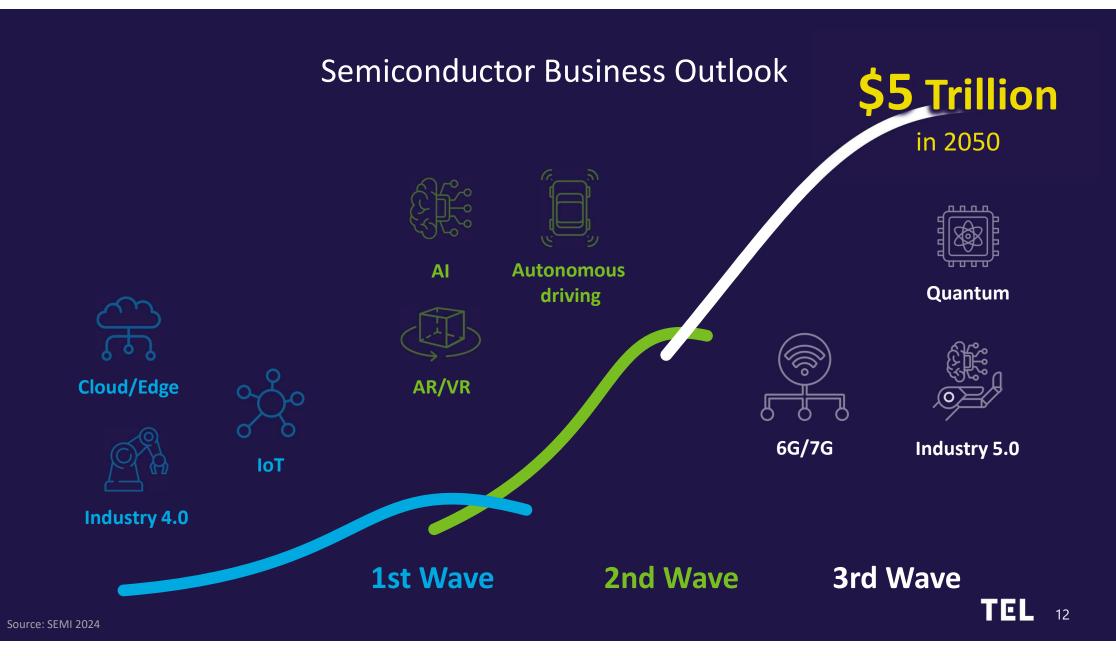

Source: SEMI 2024

Source:1990-2024 (WSTS) / 2025-2030 (IBS, January 2025)

10

#### Semiconductor Business Outlook

#### **TEL's Vision**

A company filled with dreams and vitality that contributes to technological innovation in semiconductors.

#### Innovation

Contributing to technological innovation in semiconductors

#### Profitability

Creation of social and economic value

#### People

People are at the center of everything

#### **TEL** is **Technology Enabling Life**

# CSV

#### **Creating Shared Value**

Creation of social and economic value

# TSV

### **TEL's Shared Value**

# Achieving digitalization and global sustainability

"Technological innovation in semiconductors is essential"

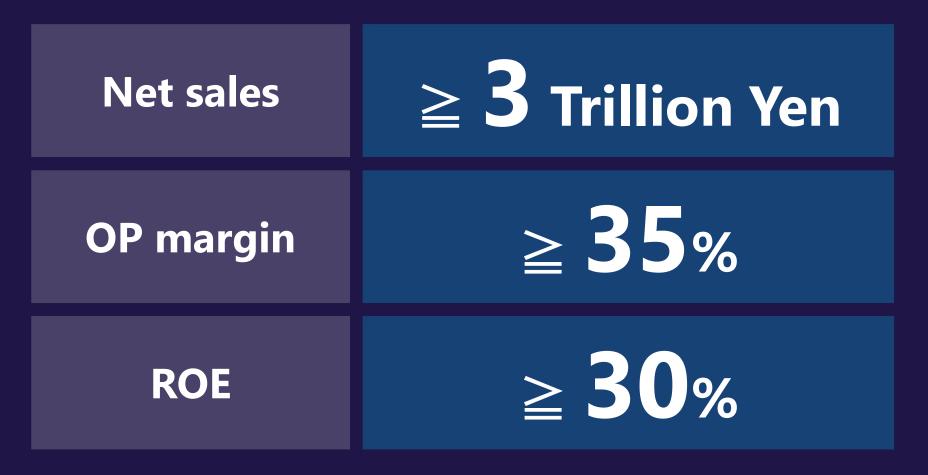

Financial Targets (by FY2027)

#### **Green Future Through Semiconductor Evolution**

# **Digital & Green**

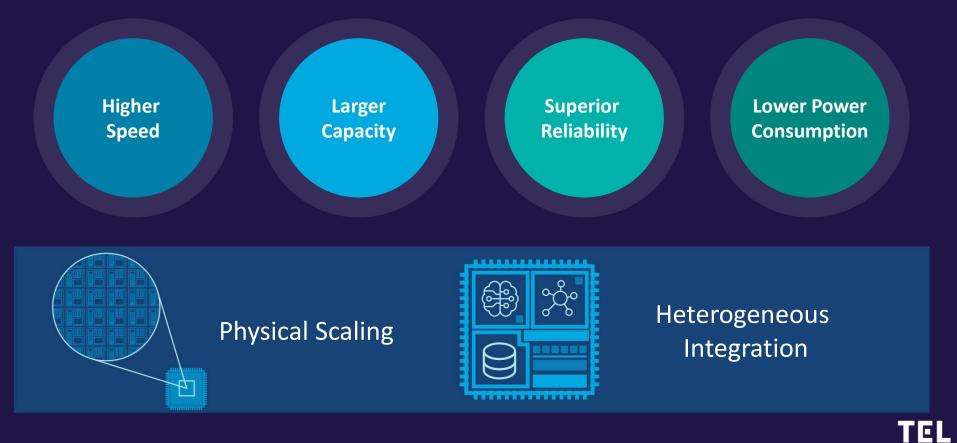

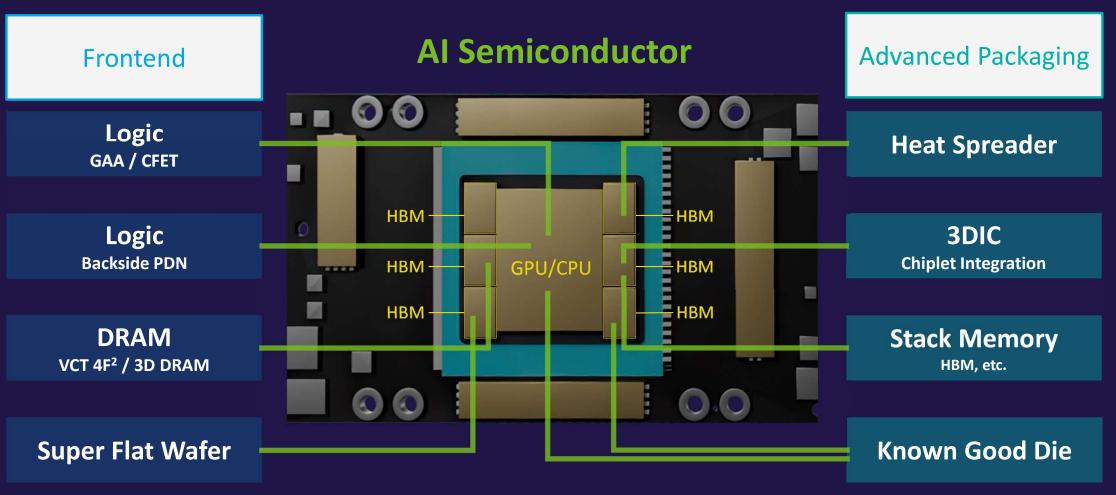

#### **Physical Scaling x Heterogeneous Integration**

\* GAA : Gate All Around

\* Backside PDN : Backside Power Delivery Network

\* VCT : Vertical Channel Transistor

**TEL** 17

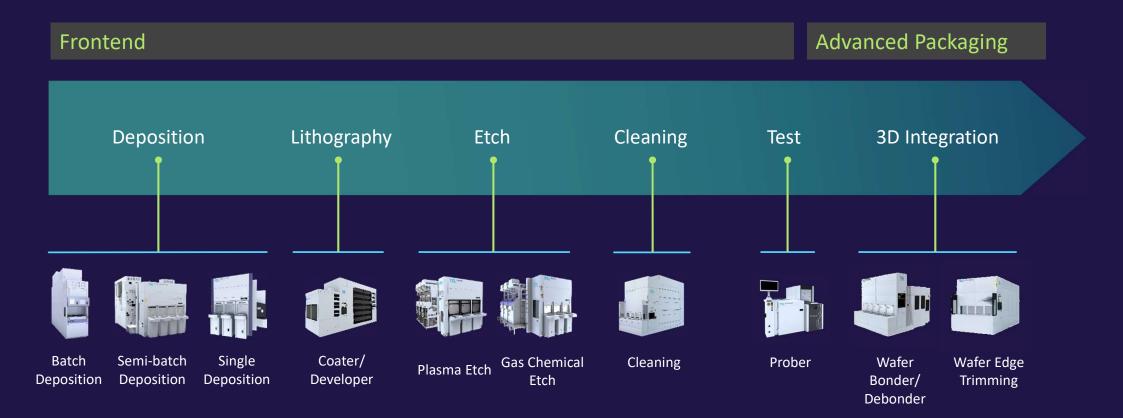

#### Expanding Opportunities : Wide Product Portfolio

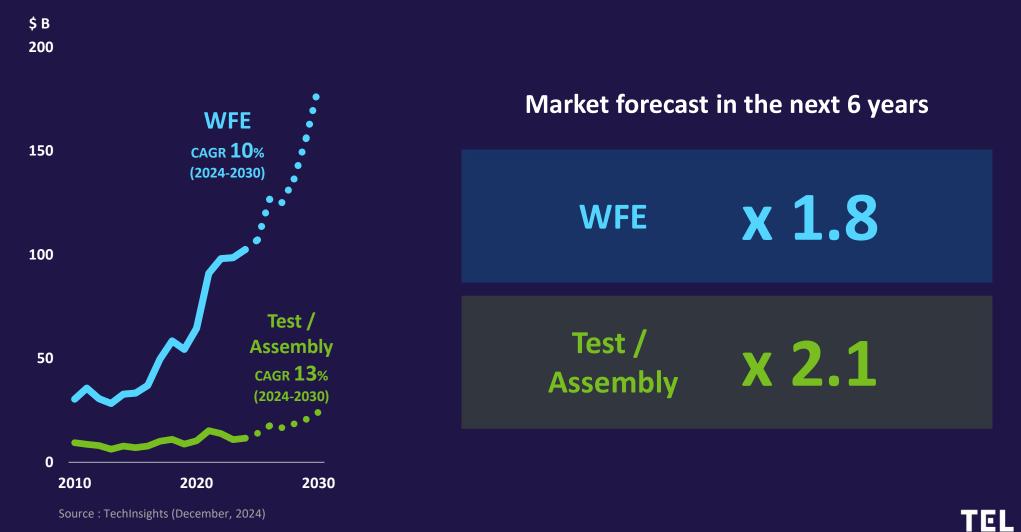

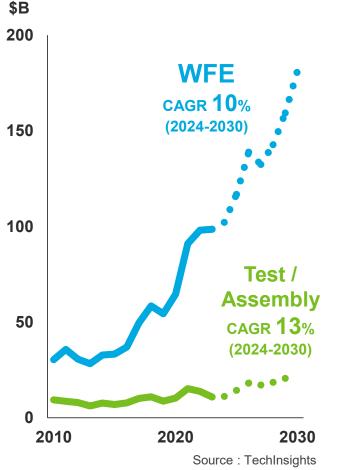

#### The Equipment Market Will Grow with the Dual Engine

19

#### The Equipment Market Will Grow with the Dual Engine

\$ B Frontend 200 NAND: beyond 4xx Logic : GAA, BSPDN DRAM: DDR5, 3D DRAM EUV Coater/Developer EUV Coater/Developer Slit Etch (major monopoly) ۲ ۲ WFE Gas Chemical Etch • Capacitor Mold Etch (major Channel Hole Etch (Plug) Conductor Etch Batch Mo deposition CAGR 10% 150 Batch High-k Capacitor deposition Batch cleaning WL Separation PVD Metal Overburden (2024 - 2030) PVD Metal Hardmask CFET/Inner Spacer Wafer Bonder Plasma CVD for filling film Supercritical Cleaning Laser Tool Double-sided scrubber Backside/bevel cleaning Backside/bevel cleaning Wafer Bonder Pattern Shaping Laser Tool 100 Wafer Bonder Laser Tool **Advanced Packaging** Test / Assembly 50 Logic Packaging **HBM Packaging** Advanced Logic / CAGR **13**% **Memory Test** Interposer, Polyimide, PR (2024 - 2030)Prober sales expected to TDV Etch Metal Etch for HBM double compared to Batch High-k Capacitor depo Aerosol Cleaning last year Wafer Bonder Temporary Bonder/Debonder 0 Laser Tool 2010 2020 2030

Source : TechInsights (December, 2024)

TEL 20

#### Investment for Future Growth (FY2025 to FY2029)

Planning proactive investments for further growth

TEL 21

#### Video : Manufacturing DX with AI and robotics

#### Aiming for the Next Generation Production

#### New Production Building Construction at Tokyo Electron Miyagi

#### **TEL's Ingredients for Success**

#### Respect for Human Rights

Climate Change and Net Zero

Product Energy Efficiency

Best Products with Innovative Technology

Best Technical Service with High Added Value

Customer Satisfaction and Trust

Supplier Relationship

Employee Engagement

Safety First Operation

Quality Management

Compliance

**Ethical Behavior**

1

Enterprise Risk Management

TEL 24

## Semiconductors Are The Future

#### Elevating Financial Position and Points for Future Growth

February 26, 2025

Hiroshi Kawamoto Division Officer, Finance Division SVP & GM

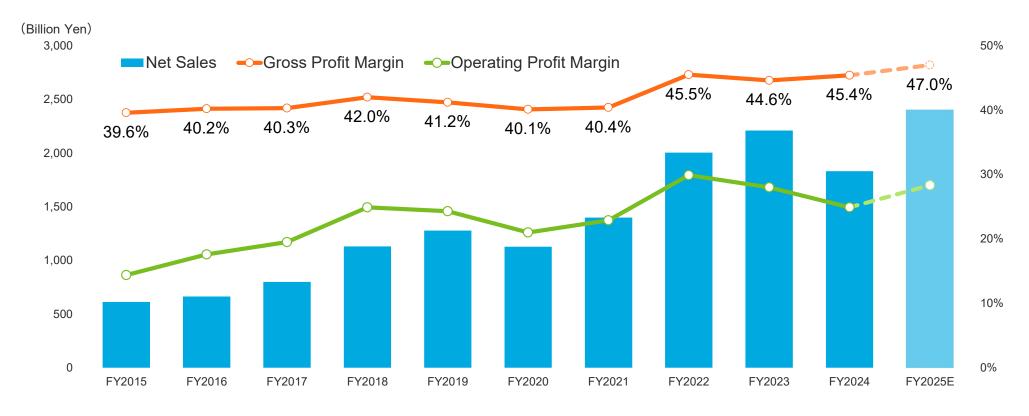

#### Net Sales and Gross Profit Margin Trend (FY2015 – FY2025)

#### Gross profit margin rose significantly on high value-added products and improved production efficiency

Investor Relations / February 26, 2025

TF

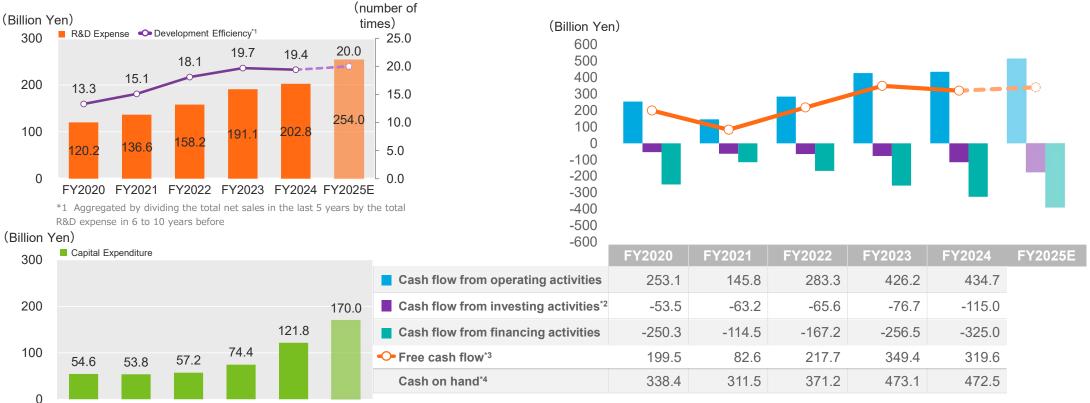

#### **Growth Investment and Cash Flow**

\*2 Cash flow from investing activities excludes changes in time deposits and short-term investments.

\*3 Free cash flow = "Cash flow from operating activities" + "Cash flow from investing activities" (excluding changes in "Time deposits" and "Short-term investments").

\*4 Cash on hand includes "Cash and cash equivalents" + "Time deposits and short-term investments" with original maturities of more than three months.

#### Robust cash flow supports aggressive growth investment

FY2020 FY2021 FY2022 FY2023 FY2024 FY2025E

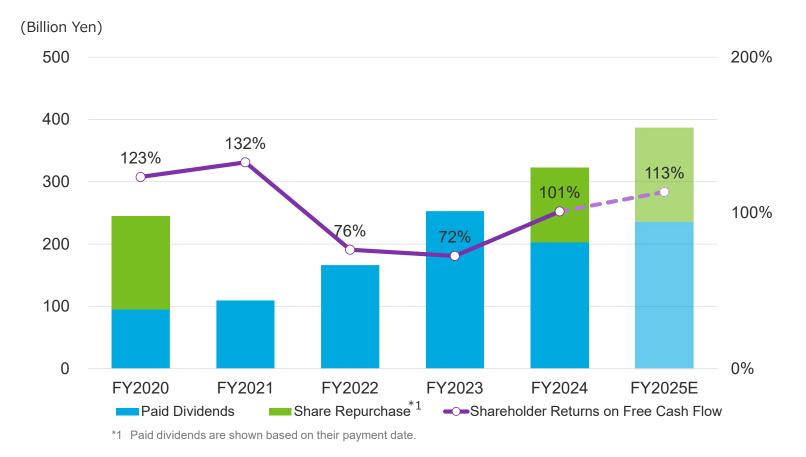

#### Shareholder Returns Trend

#### Aim for continuous high level of cash generation and shareholder returns

30

TEL

#### Summary

- Elevating gross profit margin

- High value-added products

- Production efficiency enhancement

- Continuous growth investment

- Conduct R&D/capex with an eye to market growth

- Support growth investment by robust cash flow

- Shareholder returns

- Disburse record-high shareholder returns for FY2025

- Continue to aim for high shareholder returns

#### Continue aggressive growth investment and shareholder returns through raising gross profit margin and a high level of cash generation

ТБШ

#### **Opportunities in Frontend Process Business**

#### and Activities in Digital x Green

February 26, 2025

Hiroshi (Jack) Ishida Division Officer, Frontend Process Business Division SVP & GM

#### **Challenges for the \$1 Trillion Market**

Investor Relations / February 26, 2025

ТЕ

#### Our Growth Opportunities in the Frontend Market

Investor Relations / February 26, 2025

- CAGR driven by AI-related devices to continue to drive high growth of WFE's CAGR

- Leveraging TEL's strengths to address high-growth market areas:

- Leading-edge logic: The etch market is expected to grow by 2.7 times, the deposition market by 2.5 times\*

- DRAM: The etch market is expected to grow by 2.3 times, exceeding the CAGR of WFE\*

- By introducing new products focused on the key technological inflection points, we aim to further expand our areas of entry

\* TEL Estimates

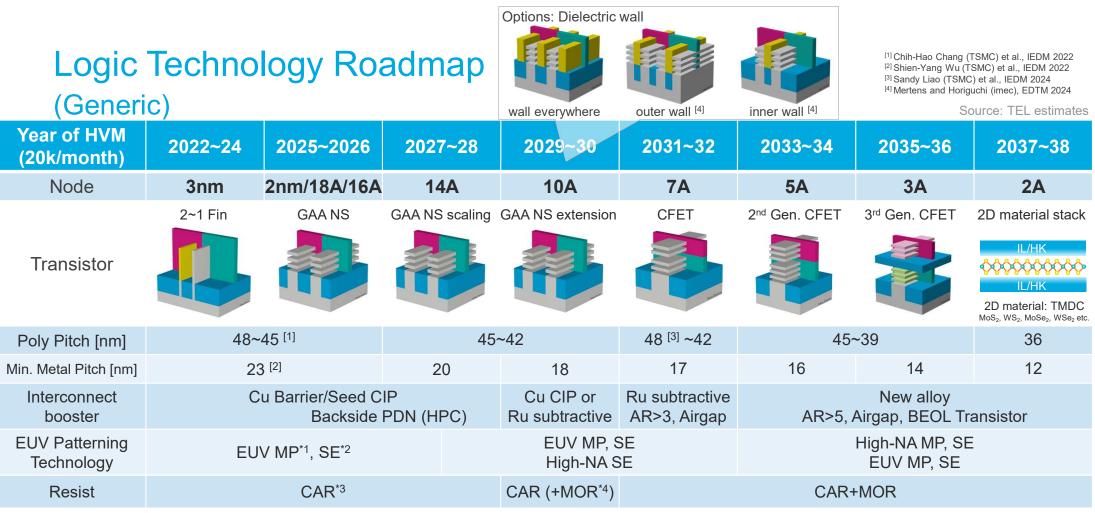

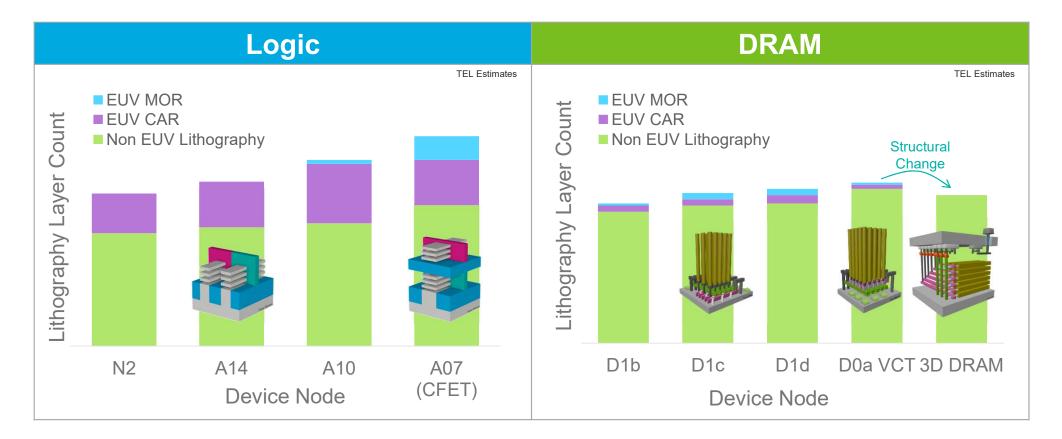

\*1 MP: Multi-Patterning, \*2 SE: Single-Exposure, \*3 CAR: Chemically Amplified Resist, \*4 MOR: Metal Oxide Resist

Logic scaling will continue by changing transistor structure and material evolution

Investor Relations / February 26, 2025

#### DRAM Technology Roadmap (Generic)

Source: TEL estimates Year of HVM 2023-24 2025 2026 2027 2028 2029 2030 2032 2034 2031 2033 2035 (20k/month) Node 1b 1c 1d **0**a **0**b **0**c **0d 0e** 2D 3D 4F<sup>2</sup> VCT\* [1,2] 6F<sup>2</sup> Cell layout / Structure \* Vertical Channel Transistor <sup>[1]</sup> Seokhan Park (Samsung) et al., IEDM 2023 <sup>[2]</sup> Daewon Ha (Samsung) et al., IEDM 2023 F [nm] in 6F<sup>2</sup> 13~12.5  $(3D \sim 1xxL)$ 12~11 10 9 8 (3D > 1yyL)7 Cap. pitch [nm] 39~37.5 36~33 30 27 24 21 Capacitor Cap. A.R. >50 >55 >65 >70 >75 >80 A.R Cap. Mat. **ZrAIHfO** Alternative (HfZrO Anti Ferro. etc) WL TiN Low R metal WL-Poly-Si HKMG Peri. CMOS FinFET Bonding HBM4E HBM5 HBM3E HBM4 HBM HBM6 HBM5E (12/16Hi,36/48GB) (16,20Hi, 64/80GB) (8/12Hi,24/36GB) (16Hi,64GB)

TEL

#### NAND Technology Roadmap (Generic)

Source: TEL estimates Year of HVM 2024 2025 2026 2028 2027 2029 2030 2031 2032 2033 2034 2035 (20k/month) Stack 3xxL 4xxL 5xxL 7xxL 1xxxL \*1yyyL \*1zzzL \*2xxxL (~1.3x/1.5years) 2 or 3 3 or 4 3 or 4 3 - 5 4 - 6 5 - 7 6 - 8 7 - 10 Tier 39 - 45 38 - 43 38 - 42 37 - 41 36 - 40 35 - 39 34 - 38 33 - 37 Vertical pitch [nm] Memory height 12 - 14 15 - 19 18 - 27 45 - 62 70 - 84 24 - 3634 - 45 57 - 74 [µm] - MILC/MIC Poly Si Resistive Ferroelectric Fe/Re Charge trap (CT) Continuous CT **CT** isolation NAND<sup>3</sup> Channel Poly Si grain CIP MILC<sup>1</sup>/MIC<sup>2</sup> TiN/W WL metal W or Mo Мо **Continuous CT CT** isolation FeNAND ReNAND #holes btw. Slits 14 - 20 19 - 25 24 - 32 30 - 36> 36 #of memory holes b/w slits Under array Bondina Vertical Pitch -Layout/Structure Bonding or Multi Bonding or Bonding Tier Peri. CMOS Poly Si Gate HKMG \* Trend Extrapolation <sup>1</sup> Metal induced lateral crystallization, N. Ishihara (Kioxia) et al., VLSI 2023 <sup>2</sup> Metal induced crystallization <sup>3</sup> Jeehoon Han (Samsung) et al., IEDM 2023 Bonding Multi Bonding 38

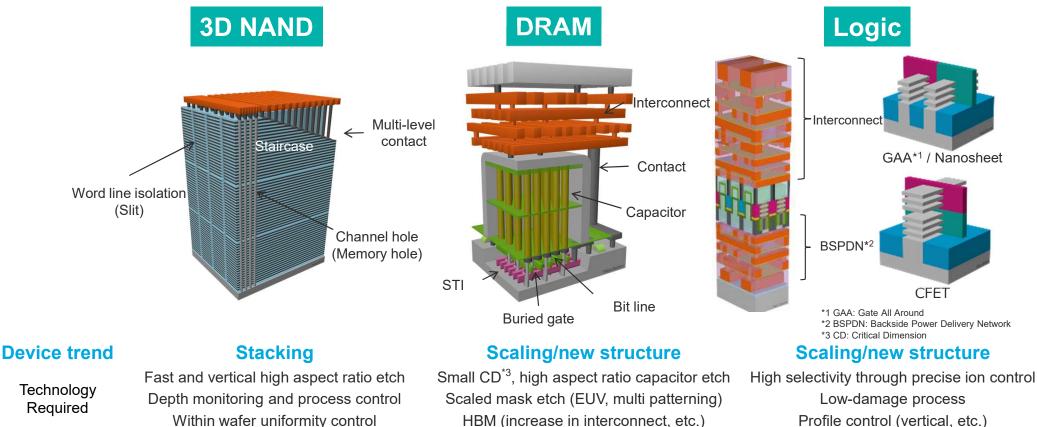

# Growth opportunities at Technological Inflection Points in Frontend Process

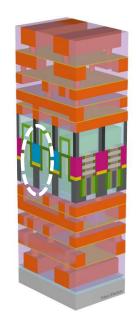

#### Logic: GAA<sup>\*1</sup>, BSPDN<sup>\*2</sup>, CFET

- Adaption of High-NA lithography, combined with multi-patterning and MOR technologies, presents opportunities for new technology Acrevia<sup>™</sup>

- Adoption of multi-patterning to increase demand for deposition, etch, and cleaning processes.

- GAA and CFET transistors to drive an increase in gas chemical etch processes

- New materials like ruthenium and structural innovations such as air gaps to generate fresh opportunities

#### DRAM: HBM, VCT<sup>\*3</sup>, 3D DRAM

- Adoption of multi-patterning driving increased demands in deposition and etch

- Capacitor formation remains essential, driving ongoing demand for advanced etch and deposition

- 3D DRAM leading to increased processes in deposition, etch and gas chemical etch

#### NAND: Beyond 4xx

- Increased layer counts leading to higher investments in deposition and etching processes

- High aspect ratio etch to become increasingly important

- New materials such as molybdenum, and low-resistance channel silicon to be utilized

\*1 GAA: Gate All Around \*2 Backside PDN: Backside Power Delivery Network \*3 VCT: Vertical Channel Transistor

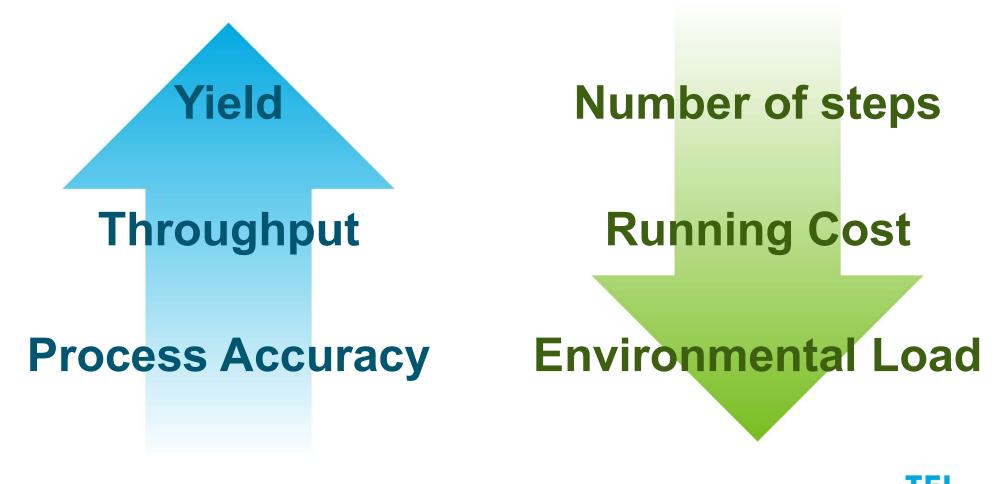

#### Provide High Value-Added Products for Sustainable Growth

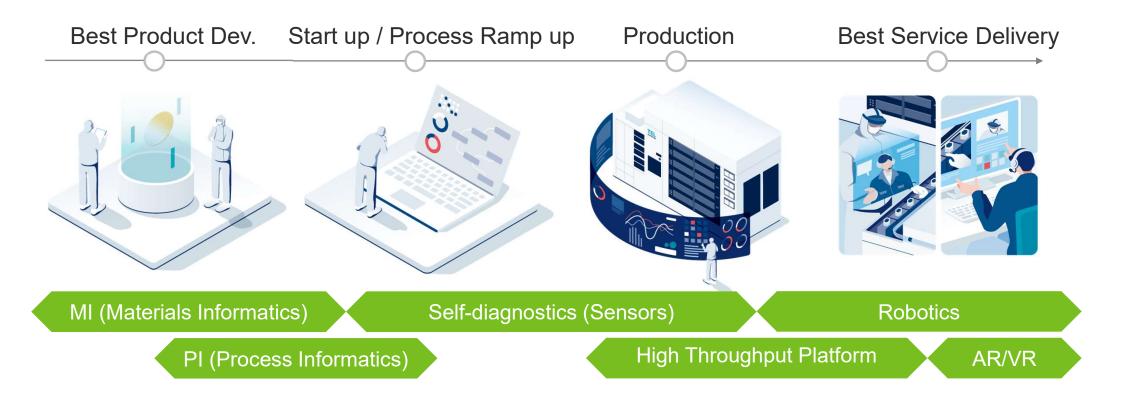

#### Leveraging Digital Transformation (DX)

#### Developing digital enablers for use throughout the business to leverage productivity and profitability

Investor Relations / February 26, 2025

41

TF

#### Leveraging Digital Transformation (DX) in Field Solutions

Maximize work efficiency for startup and maintenance in the Clean Room by using smart glasses and remote expert support. Use of AR/VR and DX including digital twin technology.

Use of robots for parts replacement without human assistance is expected to minimize downtime and improve the quality of engineering work.

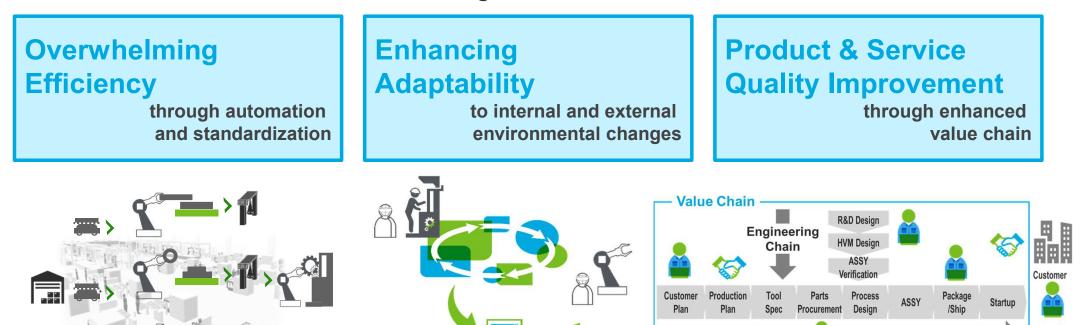

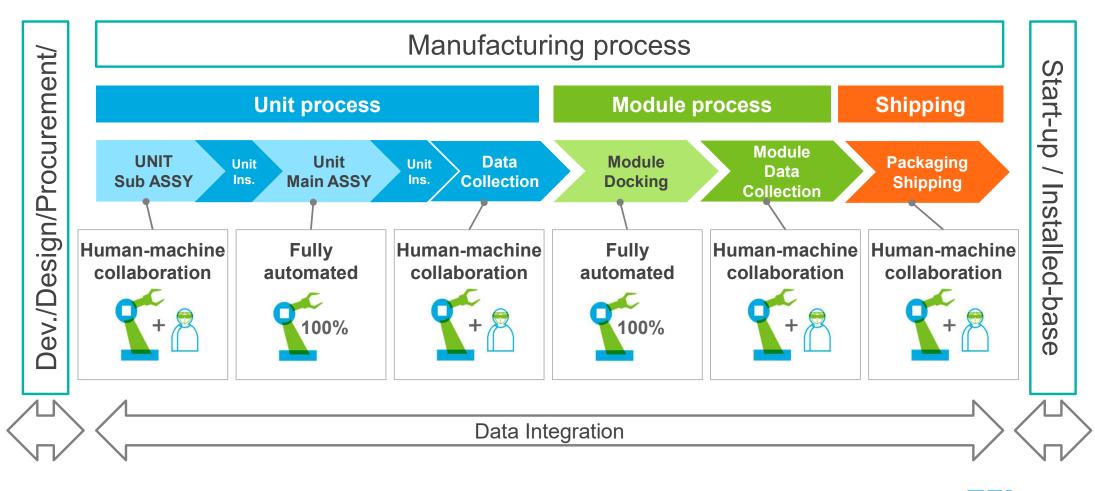

# Aiming for the Next Generation Production: New Production Building at Tokyo Electron Miyagi

#### **Vision for Smart Production**

Achieve sustainable manufacturing for the future

Supply Chain

5

#### **Concept of Smart Production**

ТБІ

#### Summary

- Aiming for further growth in frontend equipment in the volume zone of the market

- Advance the introduction of new products in growth areas related to AI

- Provide high-value-added equipment that leverages our technology in technological inflection points

- Support sustainable growth in the semiconductor market through Digital x Green initiatives

- Promote the adaption of high-productivity equipment, labor-saving techniques, process reduction, and energy-saving technologies

- Enhance productivity and profitability in semiconductor manufacturing through the implementation of DX and robotics

- Increase productivity and profitability of equipment through smart production

### Activities in Coater/Developer and Cleaning System

February 26, 2025

Yasuhiro Washio CTSPS BU VP & GM

### Coater/Developer

#### Coater/Developer: CLEAN TRACK<sup>™</sup> LITHIUS Pro<sup>™</sup> Z for EUV

LITHIUS Pro<sup>™</sup> Z released in 2012 (> 3000 systems shipped)

High Reliability High share in EUV market

#### **High Productivity**

Maximizes output of EUV lithography tools, and reduces chemical consumption

#### **High Versatility**

Supports CAR, MOR and underlayers

New features to support EUV CAR<sup>\*1</sup>/MOR<sup>\*2</sup> to be released as on an ongoing basis

\*1 CAR: Chemically Amplified Resist \*2 MOR: Metal Oxide Resist

LITHIUS Pro<sup>™</sup> Z platform with its proven mass production for various litho tools, ensures high reliability and productivity for EUV litho, along with high versatility for next-generation EUV Investor Relations / February 26, 2025

# **Outlook on Lithography Layer Count**

MOR expected for Logic 10A/ DRAM D1b, development ongoing for MOR

Investor Relations / February 26, 2025

51

TEL

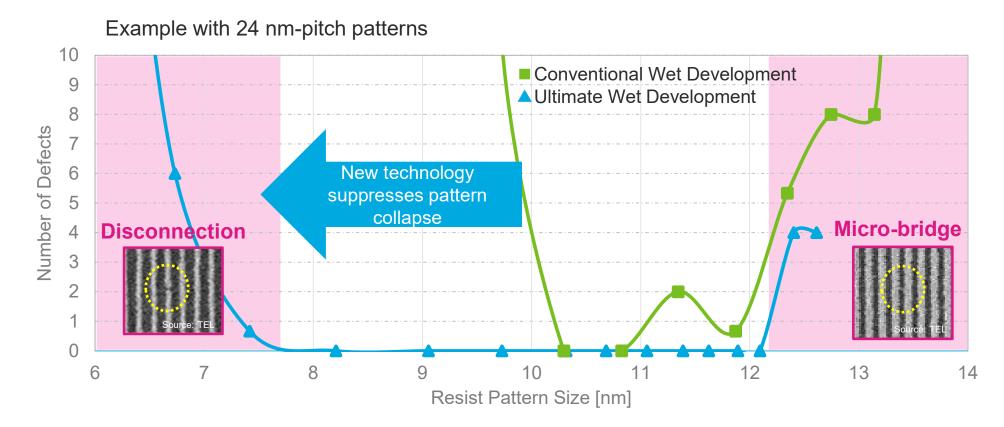

#### Example of MOR Solution: The Ultimate Wet Development

\*1 Based on internal information and development targets \*2 Based on results of developing 24 nm-pitch lines

|                                                    | Ultimate Wet<br>Development<br>Technology | Conventional<br>Wet Technology | Alternative Technology                                                      |

|----------------------------------------------------|-------------------------------------------|--------------------------------|-----------------------------------------------------------------------------|

| Base Technology                                    | Coater/Developer                          | Coater/Developer               | Etch                                                                        |

| Process Ambient                                    | Atmospheric                               | Atmospheric                    | Vacuum                                                                      |

| Reaction                                           | Chemicals                                 | Chemicals                      | Corrosive Gas                                                               |

| Throughput <sup>*1</sup>                           | 4x                                        | 4x                             | 1x                                                                          |

| Chemical Consumption <sup>*1</sup>                 | 50% (vs. conventional)                    | 100 %                          | N/A (uses gas)<br>exhaust processed<br>in combustion abatement post process |

| Anti-Pattern Collapse <sup>*1</sup><br>Performance | < 8 nm <sup>*2</sup>                      | > 10 nm <sup>*2</sup>          | < 8 nm*1                                                                    |

| Footprint <sup>*1</sup>                            | In-Line                                   | In-line                        | Additional Footprint                                                        |

Evaluation of Ultimate Wet Development ongoing with key customers, with emphasis on productivity (throughput, footprint, maintainability, utilize existing facilities)

Investor Relations / February 26, 2025

TFL

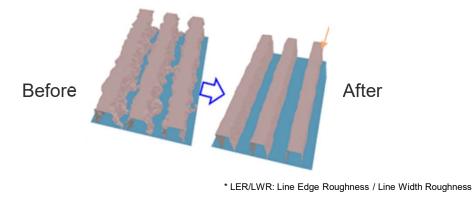

#### Example of MOR Process: The Ultimate Wet Development

The Ultimate Development technology enables the suppression of pattern collapse Investor Relations / February 26, 2025

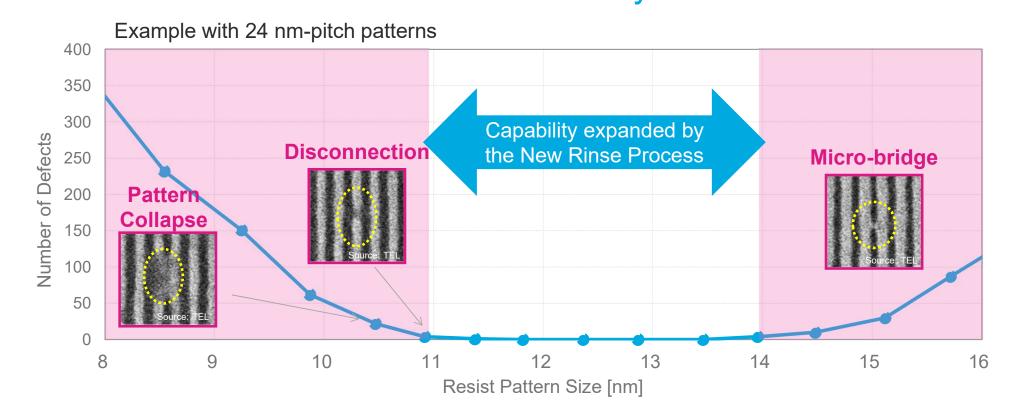

#### Example of CAR Solution: New Rinse Process and New Under Layer

The new rinse process expands the capability of CAR to be applied to smaller patterns Investor Relations / February 26, 2025

### **Cleaning System**

#### **Development of Cleaning Systems**

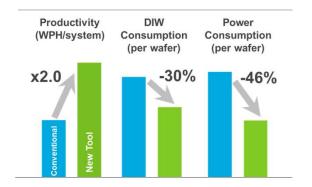

#### High Productivity Wet Bench (EXPEDIUS<sup>™</sup>-R)

Industry's first large-batch process (increased wafer counts)

Investor Relations / February 26, 2025

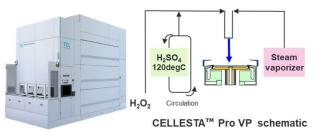

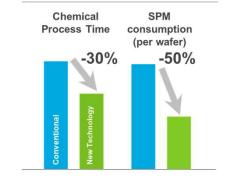

#### SPM<sup>\*1</sup> Vapor Technology (CELLESTA<sup>™</sup> Pro VP)

Enabled higher temperature process due to a more effective rection by adding water vapor to chemicals

\*1 SPM: Sulfuric Acid and Hydrogen Peroxide Mixture

#### Simultaneous Scrubber (CELLESTA™ MS2)

A tool enabling AS<sup>\*2</sup> process on wafer frontside and physical brushing process on wafer backside simultaneously in a single chamber \*2 AS: Atomized Spray

> Productivity (WPH/system) Cost of Ownership (per wafer) x2.0 Image: Cost of Ownership (per wafer)

> > 56

TEL

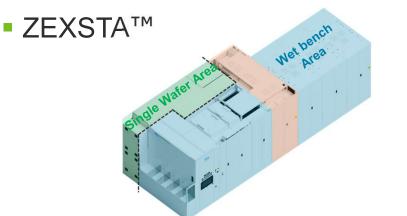

# New Cleaning Tool: ZEXSTA<sup>™</sup>

A combination of wet bench + single-wafer process

| Method          | Features                                     |

|-----------------|----------------------------------------------|

| Wet<br>Bench    | High-temp/ long-duration process, wet etch   |

| Single<br>Wafer | Advanced drying technology, particle control |

- Target Application

- Advanced wet etch + advanced dry tech

- Highly selective wet etch process will be required for also 3D DRAM in addition to 3D NAND

- High throughput + surface cleanliness

High surface cleanliness is required for logic and DRAM

57

TEL will contribute to customer technology development by continuing to create new value, overcoming the constraints of traditional equipment classifications TEL

# Latest Technological Challenges and Activities in Etch

February 26, 2025

Tetsuya Nishiara ES BU VP & GM

#### **Requirements and Various Etch Technologies**

HBM (increase in interconnect, etc.)

Profile control (vertical, etc.)

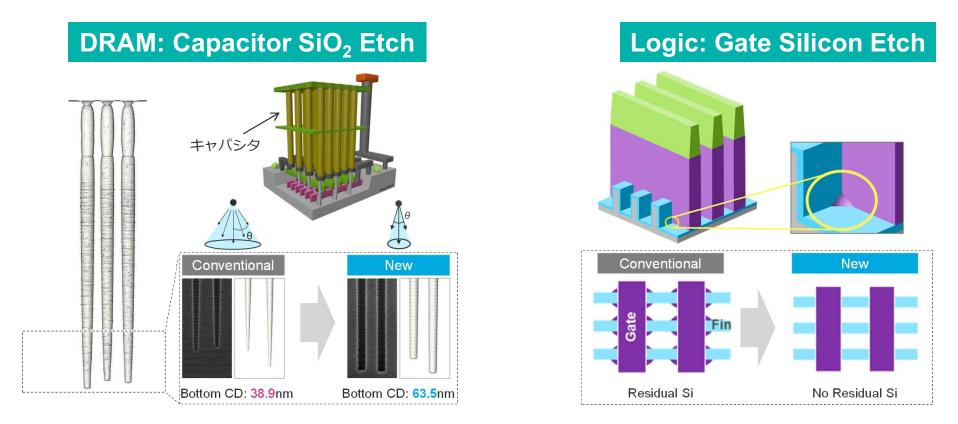

Etch technology with precise controllability is required for further evolution of devices

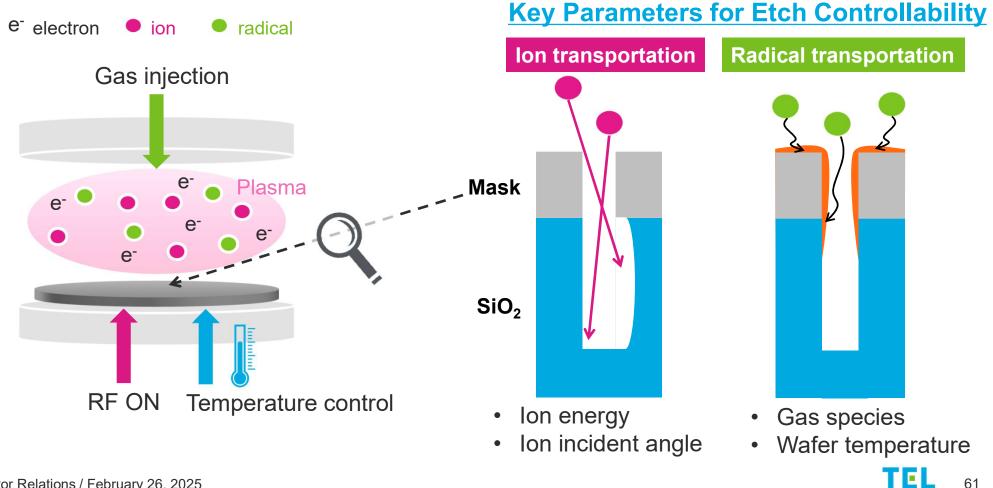

#### **Overview of Etching and Key Parameters**

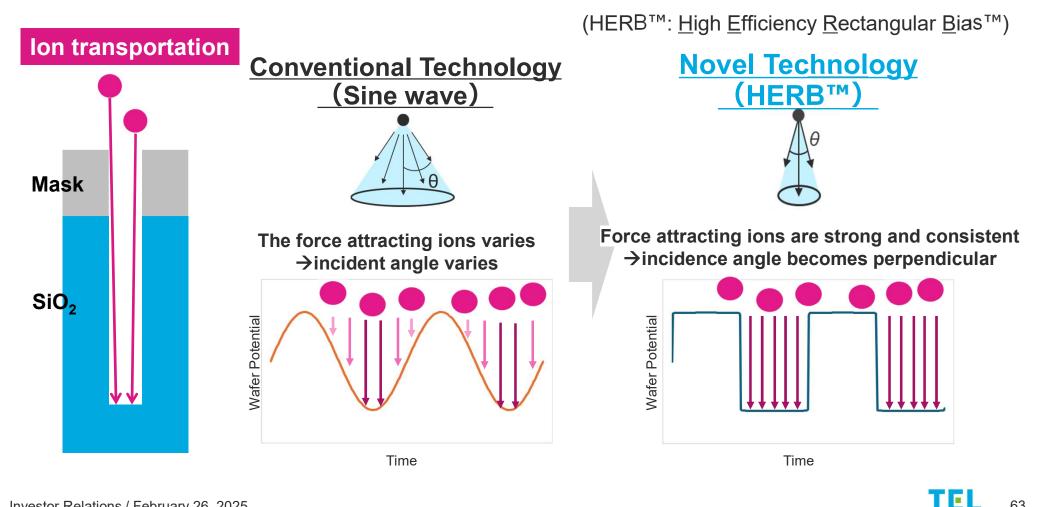

# Our Unique Technology 1: HERB<sup>™</sup>

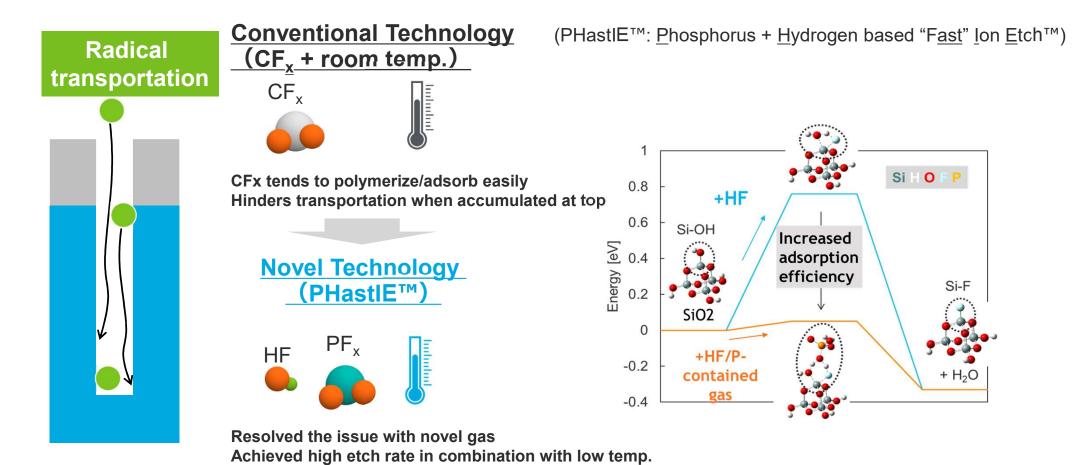

#### Our Unique Technology 2: PHastIE<sup>™</sup>

TEL

65

# PHastIE<sup>™</sup>

Less Deposition by **New Chemistry**

Sidewall Protection by **Cryogenic Temp Control**

Higher Etch Rate by **New Chemical Reaction**

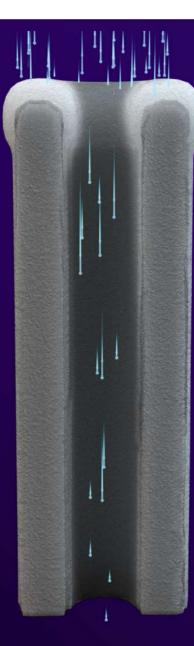

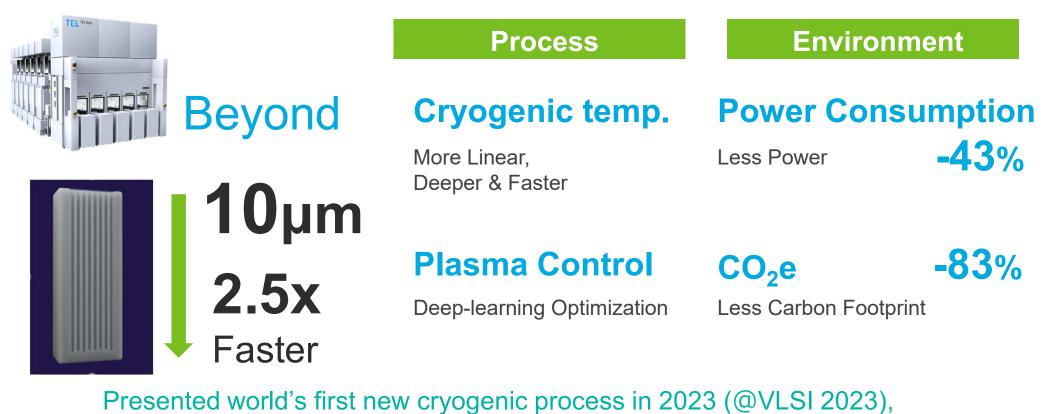

# TELAVES<sup>™</sup> for Novel Cryogenic HARC Etch

achieving both high process and environmental performance

#### Future of New Etch Technologies

New technologies created through the development of ideal etching process development, will be applied to a variety of critical processes

Investor Relations / February 26, 2025

ТЕ

#### **Development Eco System for Further Growth**

- Continuously creating industry-first technologies through a development ecosystem involving suppliers, universities and TEL

- The development of sustainable solutions through this ecosystem is the source of our competitive advantage

- The Miyagi Technology Innovation Center in TEL Miyagi plays a key role

### Smart Manufacturing to Achieve High Quality and Productivity

# Development & Design Sub-Assembly Inspection Feed Forward Feedback

By centralizing development and production in TEL Miyagi, we ensure continuous concurrent engineering and advanced manufacturing capabilities

Our mission:

To continue developing supreme etching technology that exceeds our customers' imaginations, and to continue to deliver it in a timely manner.

### Business Strategy in Thin Film Deposition

February 26, 2025

Shigeki Nakatani TFF BU VP&GM

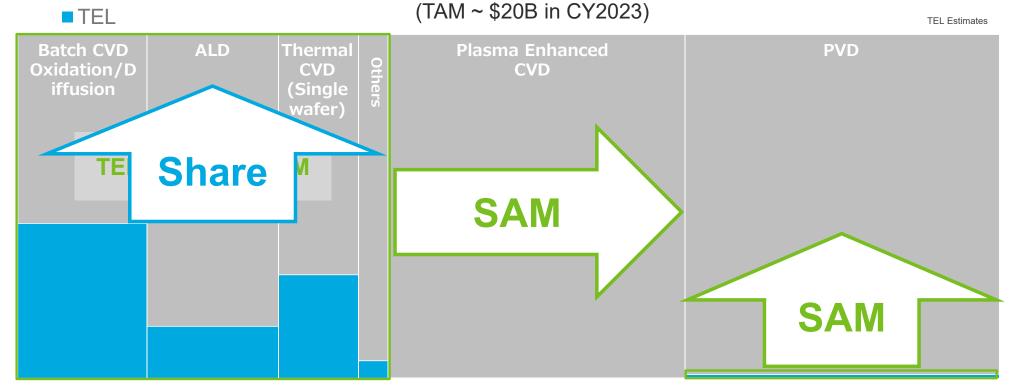

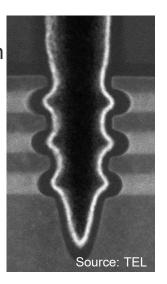

#### Business Strategy in the Thin Film Deposition Market Expanding Market Share and SAM<sup>\*</sup>

TEL's Market Share and SAM in Thin Film Deposition

\* SAM: Served Available Market

## Strategies in the Film Formation Business 1:

Expand SAM Using Single Wafer Deposition Equipment

Triase<sup>+™</sup>

Single Reactor Existing Platform

Episode<sup>™</sup> 1

Single Reactor Equipped with up to eight process modules

#### Released in July 2024

Episode™ 2 DMR\*

\*Duo Matched Reactor

Achieved high productivity by processing 2 wfs/PM

#### Episode™ 2 QMR

#### **Quad Matched Reactor**

Equipped with a newly developed high-density plasma source

#### Scheduled for release in 2026

### Video

## Strategies in the Film Formation Business 1:

Expand SAM Using Single Wafer Deposition Equipment

Single Reactor Existing Platform

Episode<sup>™</sup> 1

Single Reactor Equipped with up to eight process modules

#### Released in July 2024

Episode™ 2 DMR\*

\*Duo Matched Reactor

Achieved high productivity by processing 2 wfs/PM

#### Episode<sup>™</sup> 2 QMR

#### **Quad Matched Reactor**

Equipped with a newly developed high-density plasma source

#### Scheduled for release in 2026

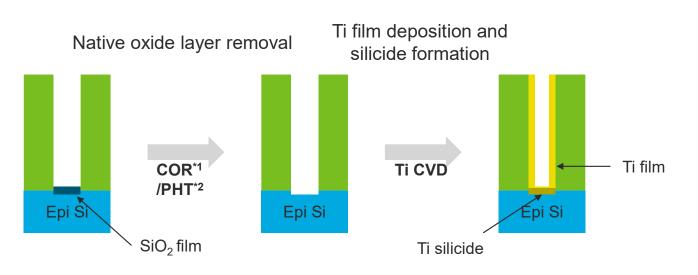

#### Episode<sup>™</sup> 1: Contact Formation Process

#### Example of process flow

\*1 COR: Chemical Oxide Removal \*2 PHT: Post Heat Treatment

Multiple types of process modules are equipped on a high-vacuum transfer module, and low-resistance contacts are achieved by sequentially processing native oxide layer removal and metal film formation

Investor Relations / February 26, 2025

TFL

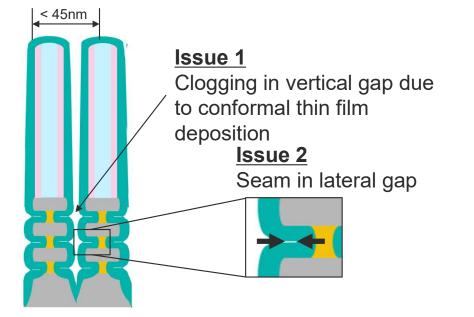

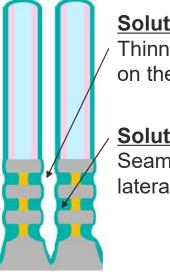

### Episode<sup>™</sup> 1: Inner Spacer Formation - Lateral Gapfill

#### Issues :

Leak due to dielectric breakdown due to etching

Solutions : Improve lateral gapfill performance

<u>Solution 1</u> Thinner film deposition on the side walls

<u>Solution 2</u> Seamless gapfill in lateral gap

Realized seamless lateral gapfill using a unique thin film deposition technique and laterally uniform film modification using a newly developed high-density plasma Investor Relations / February 26, 2025

### Episode<sup>™</sup> 2: Performance Comparison

|                                   |                               |                                       | Triase+™           | Episode™ 2 DMR                       |

|-----------------------------------|-------------------------------|---------------------------------------|--------------------|--------------------------------------|

|                                   |                               |                                       |                    |                                      |

|                                   | Productivity and<br>Footprint | Productivity per system               | 1<br>4PM/4-reactor | 1.5<br>3PM/6-reactor                 |

|                                   |                               | Footprint                             | 1                  | 0.65                                 |

|                                   |                               | Productivity per unit area            | 1                  | 2.31                                 |

|                                   |                               | Throughput                            | 1                  | ~ 1.8                                |

|                                   | Operation                     | Process knobs                         | $\checkmark$       | 1.5<br>3PM/6-reactor<br>0.65<br>2.31 |

| 13.3                              | Operation                     | Construction cost for facilities      | 1                  | 0.64*                                |

| $\langle \hspace{-0.6ex} \rangle$ | Application                   | Legacy to leading-edge nodes          | $\checkmark$       | $\checkmark$                         |

| $ \rightarrow $                   |                               | New features for cutting-edge devices | N/A                | ✓                                    |

|                                   | Smart Function                | Data logger                           | N/A                | $\checkmark$                         |

|                                   |                               | Intelligent controller                | N/A                |                                      |

|                                   | Environmental<br>Performance  | Power consumption per wafer           | 1                  | 0.75                                 |

TEL

### Strategies in the Film Formation Business 2: SAM Expansion with PVD

LEXIA<sup>™</sup> -EX Released in December 2024

- Oblique angle sputter with wafer rotation system

- Excellent thickness uniformity (1 $\sigma$  0.5%)

- Unique multi-cathode<sup>\*1</sup> configuration

- High deposition rate

- Capability of tuning film composition ratio with multiple materials

- High throughput (~100WPH)

- Significant footprint reduction vs conventional model

\*1 Cathode: An electrode for material deposition \*2 dPVD: Dual cathode PVD \*3 mPVD: Multiple cathode PVD

#### Strategies in the Film Formation: Growth in Batch Thermal Process/Deposition

- Major applications

- Silicon process in general (dummy gate, channel Si, etc.)

- Batch ALD high-k (capacitor dielectric)

- Plasma/Thermal ALD-SiN/SiO<sub>2</sub>

- Batch molybdenum (word line)

- Development plans

- Increase load port size (8 lots, 200 wafers/batch)

- Improve exhaust conductance to mitigate pattern loading effect

- Enhance energy efficiency (elevate heater performance)

- Enhance labor reduction (one-touch start-up, self-maintenance, DX)

#### TELINDY<sup>™</sup> PE-II

#### Business Strategy in the Thin Film Deposition Market Expanding Market Share and SAM<sup>\*</sup>

TEL's Market Share and SAM in Thin Film Deposition

\* SAM: Served Available Market

### **Diverse Systems and Solutions**

February 26, 2025

Hiroshi (Kan) Ishida DSS BU VP & GM

Confidential

### Video

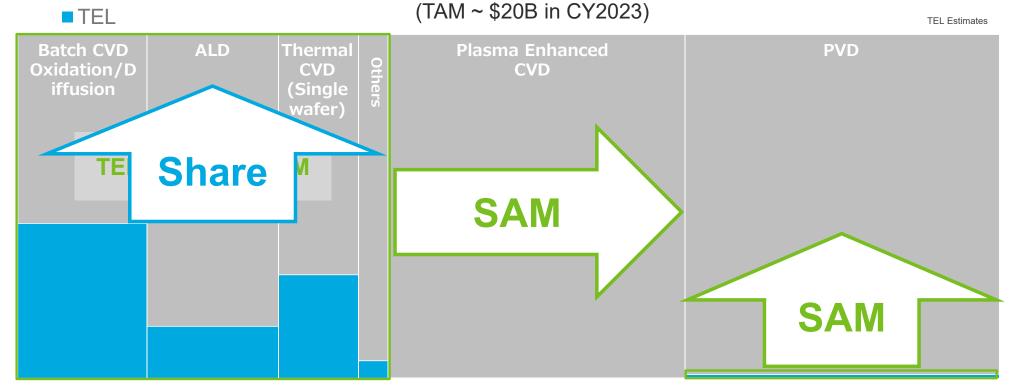

#### Acrevia<sup>TM</sup> TEL Original Gas Cluster Beam (GCB) System

- Beam Angle is freely Adjustable

- LSP (Location Specific Processing) Wafer Scan

- $\rightarrow$  Enable 3Dimetional Etching

- Drastically Improve EUV productivity by EUV step reduction with fine patterning

- Realize yield by removing defect between pattern and improving LER/LWR\*

| v |

|---|

|   |

#### TEL Manufacturing and Engineering of America, Inc.

- Gas Cluster Beam (leading-edge patterning)

- Low-damage physical cleaning (HBM, advanced packaging, etc.)

- Development of unique products for leading-edge processes

Manufacturing: Chaska, MN

R&D: Chelmsford, MA

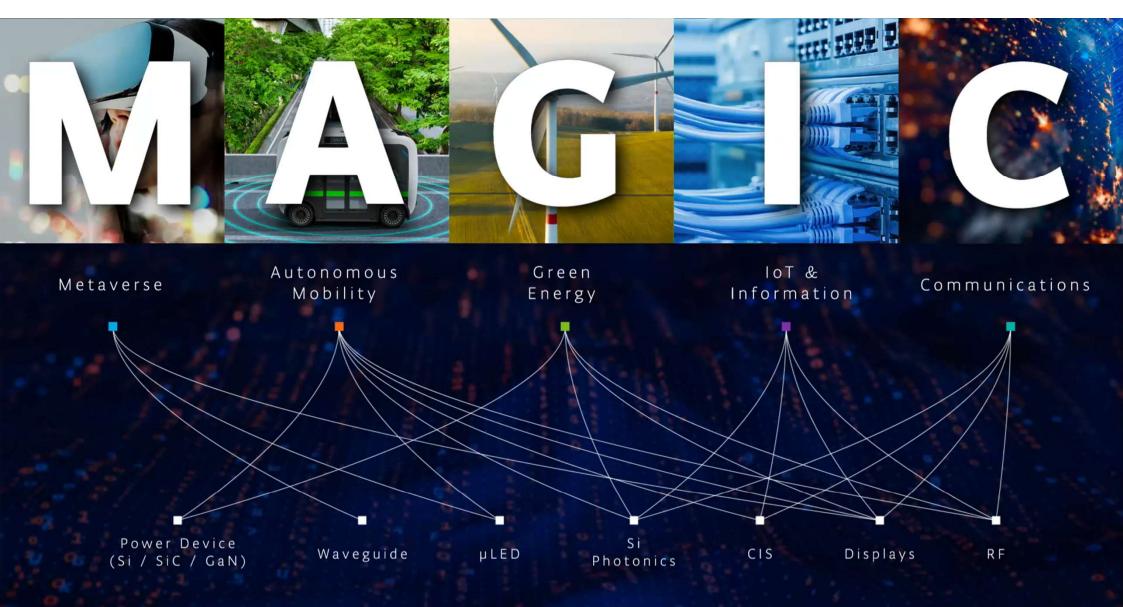

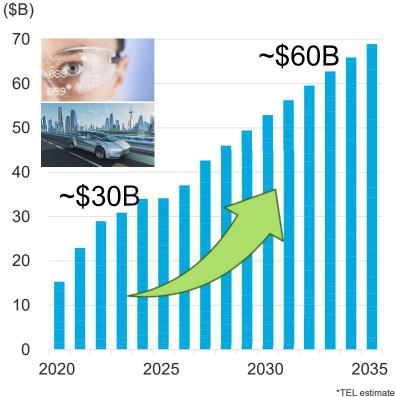

#### **MAGIC Market**

- MAGIC Market to double

- Development & sales for MAGIC specialty applications

- Demo line ready for 200mm MAGIC

- ✓ Yamanashi, Kumamoto, Miyagi

- ✓ Massachusetts, Minnesota, Florida

#### Market Estimates

Investor Relations / February 26, 2025

ТГ

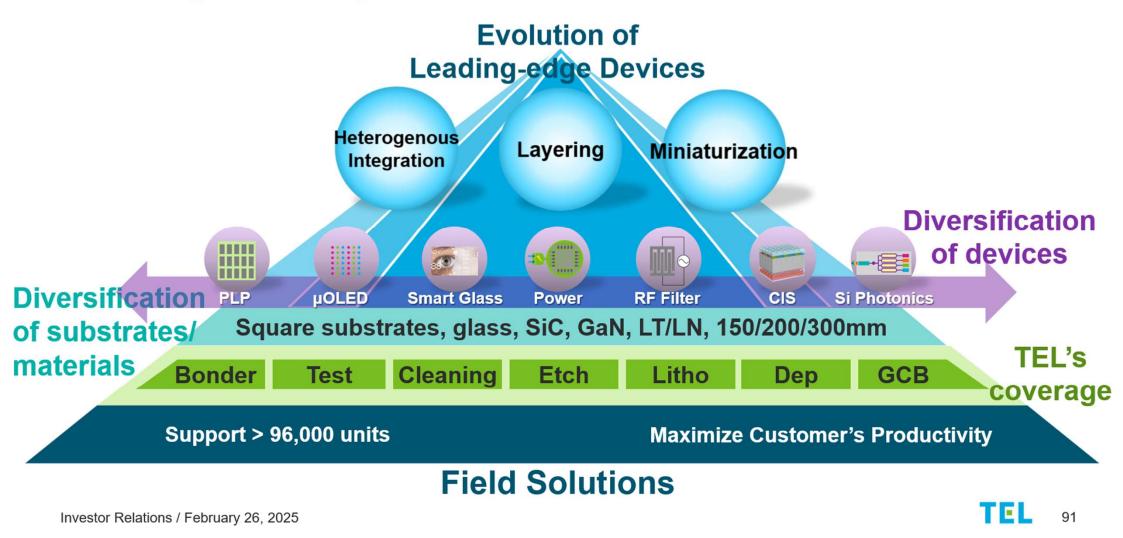

#### **Providing Diverse Systems and Solutions for Diverse Needs**

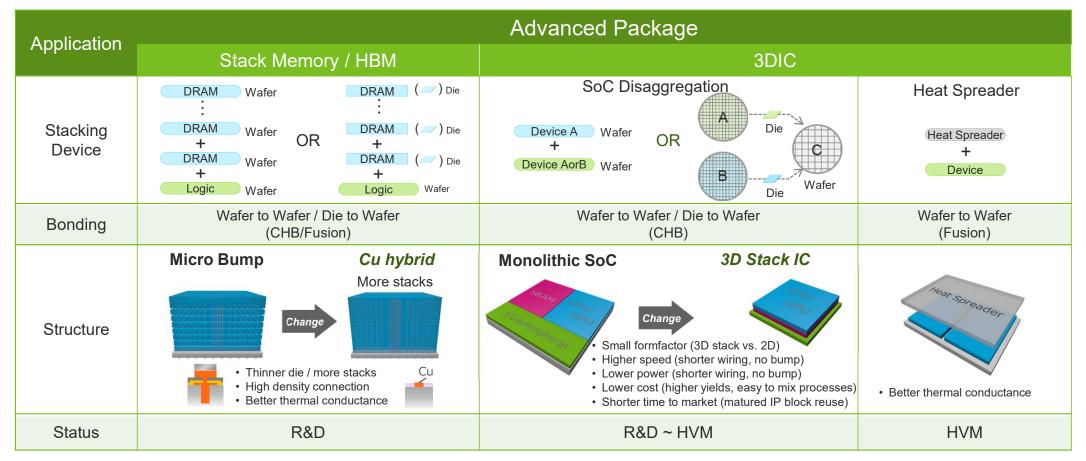

### Technology Trends and Business Opportunities in Assembly Processes

February 26, 2025

Keiichi Akiyama Division Officer, Backend Process Business Division SVP&GM

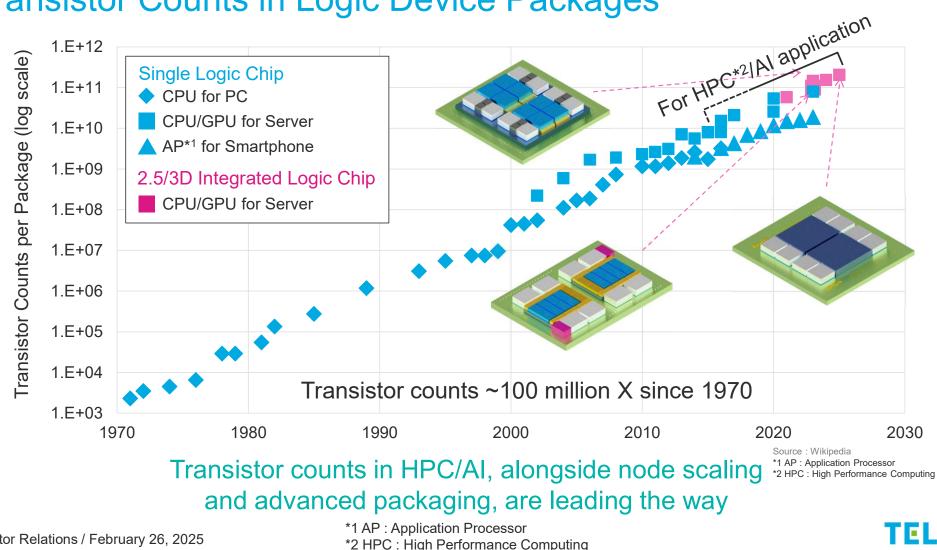

#### **Transistor Counts in Logic Device Packages**

94

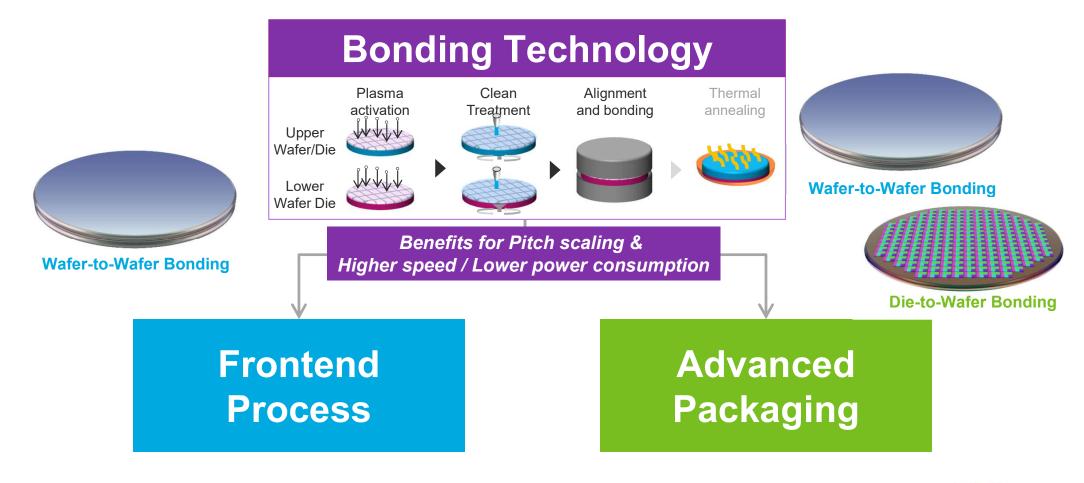

### **TEL's Opportunities for Bonding Technology**

Investor Relations / February 26, 2025

**TEL** 95

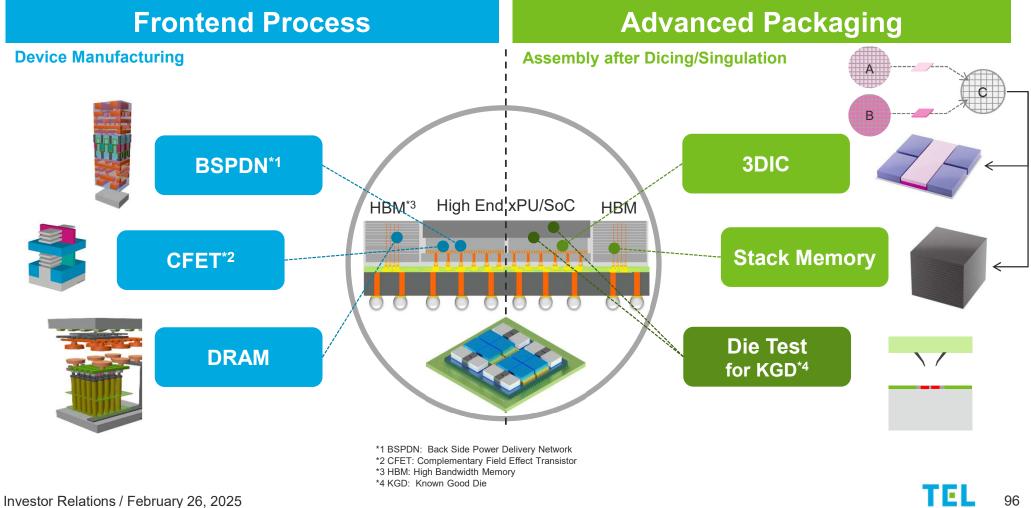

### 3DI / Test Business Expands Opportunities for HPC/AI Device

#### Frontend Process : Wafer-to-Wafer Bonding

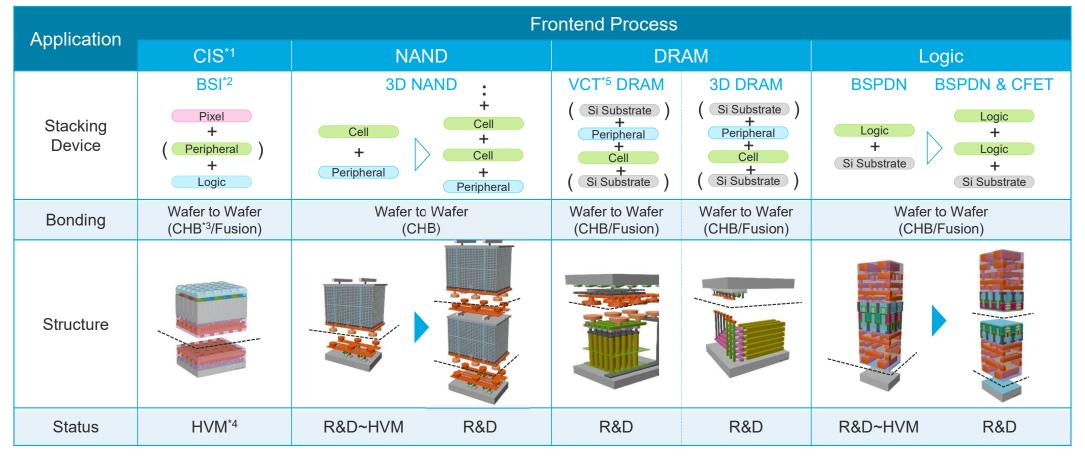

#### **Broad Applications and Expansion of Bonding Technology**

#### The design of future devices is transitioning from single bonding to multi-bonding structures

Investor Relations / February 26, 2025

\*1 CIS: CMOS Image Sensor \*2 BSI: Backside Illumination \*3 CHB: Cu Hybrid Bonding \*4 HVM: High Volume Manufacturing \*5 VCT: Vertical Channel Transistor

### Advanced Packaging : Wafer-to-Wafer / Die-to-Wafer Bonding

### **Broad Applications and Expansion of Bonding Technology**

The opportunity for CHB/fusion bonding is growing to encompass advanced packaging

Investor Relations / February 26, 2025

**I** 100

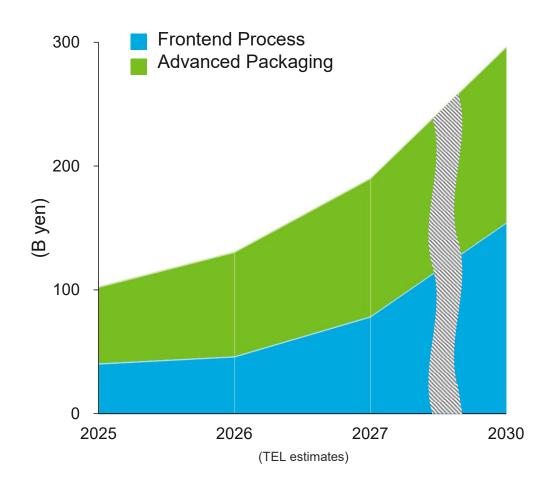

### **Bonding Process Equipment TAM\***

# Anticipating a TAM CAGR of 24% from CY2025 to CY2030

- Projected to achieve 300 billion yen by CY2030

- Encompassing both frontend processes and advanced packaging equipment

- Addressing bonding/debonding, slicing, and thinning process equipment utilizing various technologies

\* TAM : Total Available Market

TFL

101

#### Today's Message

- Bonding processes are at a critical inflection point for nextgeneration device manufacturing and advanced packaging, and further technological innovation is required to achieve this

- TEL has the advantage of covering all the technologies necessary to realize bonding technology under one roof, and has established a system to quickly respond to customer expectations

- Engagement with customers is progressing smoothly through our strategy, which places our R&D centers near the R&D bases of major customers

- We accelerate evaluation with customers' devices towards mass production

TEL Technology Center, Korea

TEL Technology Center, America

Tokyo Electron Kyusyu Limited

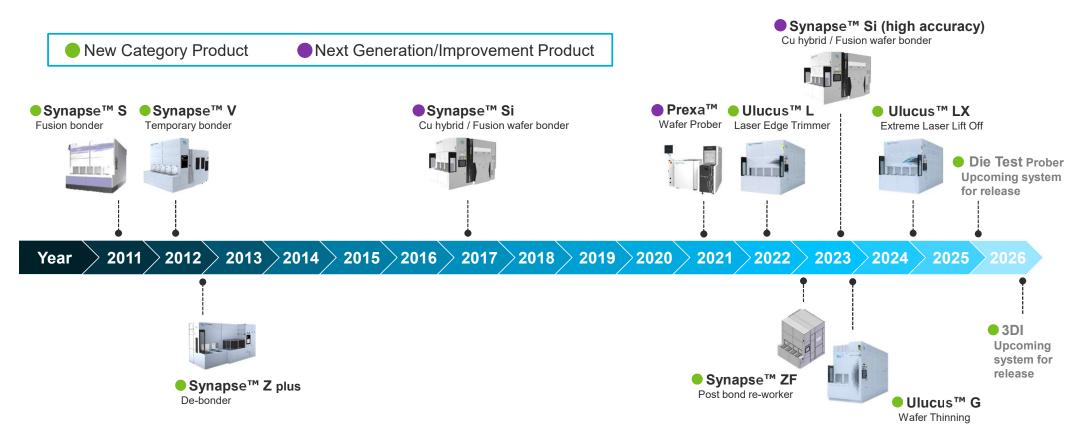

### Product Strategy in Assembly Processes

February 26, 2025

Yohei Sato ATS BU VP & GM

#### History of Product Launches in Assembly and Test\* Systems

#### Accelerating product development to prepare for the era of 3D integration

\*Test : Prober for Advanced Packaging Test

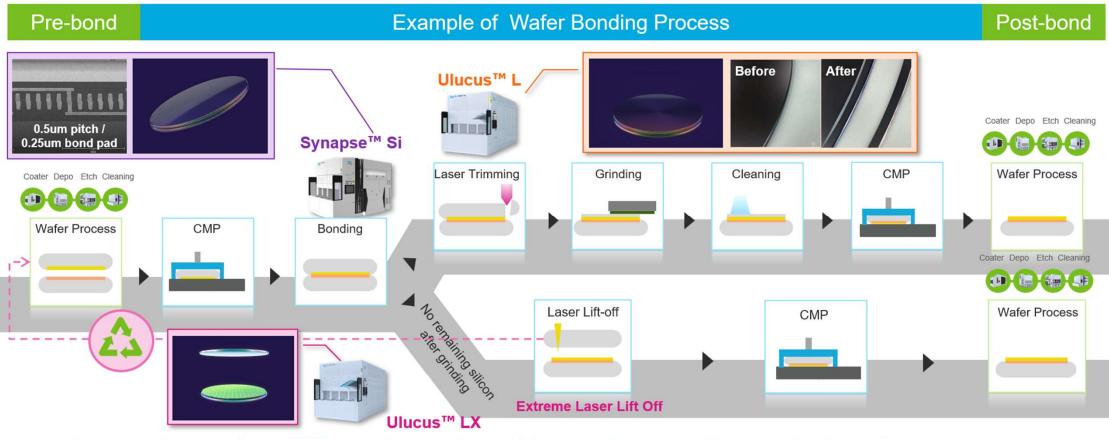

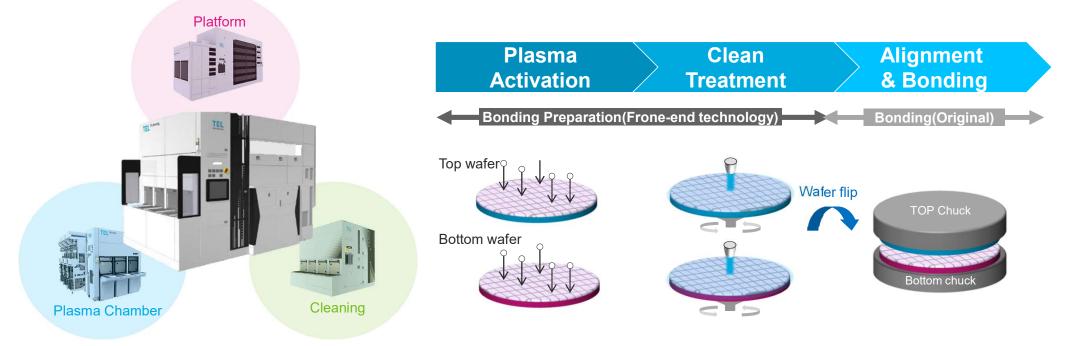

#### Frontend Wafer Bonding Process and TEL Products

Integrating various TEL equipment enables next generation wafer bonding processes that deliver high performance and process efficiency TEL

Investor Relations / February 26, 2025

106

### Wafer-to-Wafer Permanent Bonder Synapse<sup>™</sup> Si

- TEL's existing broad technology and business contributing effective product development/CIPs

- Making good progress with major memory, logic customers towards high volume manufacturing

- Leading W2W Fusion/Cu hybrid bonding technology for next generation device manufacturing

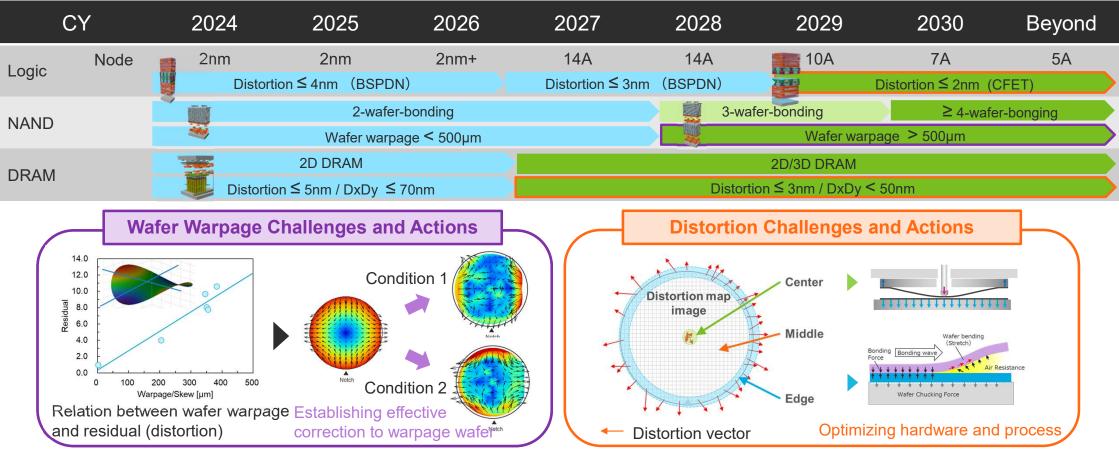

### Wafer Bonder Technology Roadmap and Challenges

TEL is developing various technologies in advance to prepare for next-generation devices Investor Relations / February 26, 2025

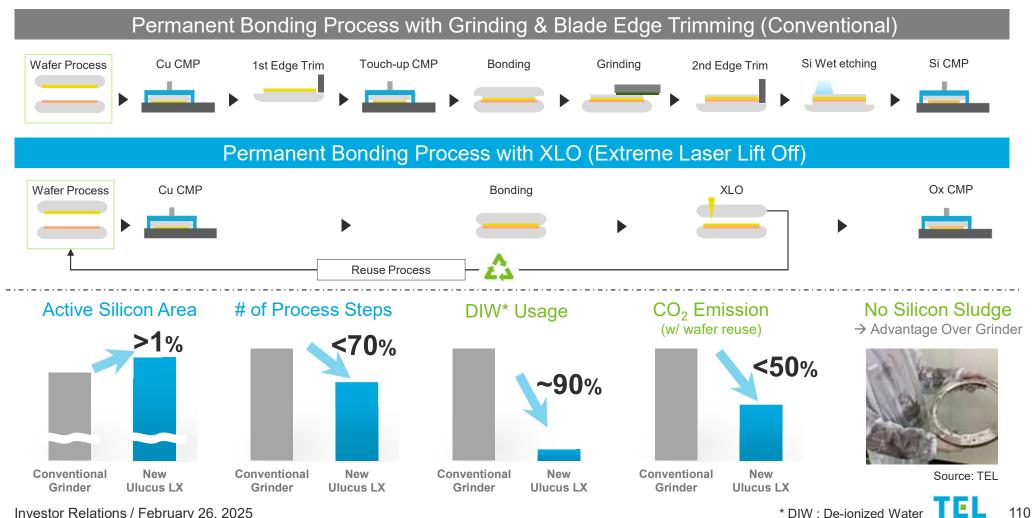

#### Introducing Ulucus<sup>™</sup> LX for Post-Wafer Bonding Process

Tokyo Electron Launches Ulucus™ LX, an Extreme Laser Lift Off System for 300mm Wafer-Bonded Devices

Tokyo Electron (TEL; Head Office: Minato-ku, Tokyo; President: Toshiki Kawai) today announced the launch of Ulucus<sup>™</sup> LX, an Extreme Laser Lift Off system for 300mm wafer-bonded devices.

With the advent of the AI era, the need to improve the performance and energy efficiency of semiconductor devices is more pressing than ever. As a result, 3D integration using permanent water bonding technology has become essential to the continued evolution of semiconductor devices. As a critical technology for high degrees of integration along with device scaling, permanent water bonding is increasingly in demand for the production of diverse semiconductor devices. These devices often require multiple bonding processes, making the technology hurdle even more challenging. Under these circumstances, the polishing and grinding steps to remove the unnecessary portion of silicon wafers requires a large amount of DI water during processing, and leads to reduced yield and a limitation on the number of available chips. Instead, an innovative technology is needed that contributes both to sustainability and productivity improvement.

Ulucus™ LX is an innovative system designed to meet this need, featuring TEL's Extreme Laser Lift Off technology and capable of performing laser beam irradiation, wafer removal, and wafer cleaning in a single unit. The system integrates TEL's advanced laser control and wafer separation expertise, with the cleaning technologies cultivated in its single-wafer cleaning systems (NS and CELLESTA™ series) and the LITHIUS Pro™ Z Coater/Developer platform that has a large installed base.

Customers using this system will be able to replace multiple processes in permanent wafer bonding, including wafer backgrinding, polishing, and chemical etching, while reducing deionized water consumption by more than 90%. By eliminating the need for conventional edge trimming, the system also increases the number of viable chips per wafer. In addition, TEL is developing the technology to reuse the excess silicon wafers removed by this system.

"In addition to scaling, the accelerating adoption of 3D high-density packaging is further evolution of semiconductor performance," said Yohei Sato, General Manager of ATS BU at TEL. "Wafer bonding is one of the most critical steps in 3D packaging. Of particular interest is the post-bonding wafer thinning process, where there are high expectations for a technological breakthrough. The newly released Ulucus<sup>74</sup> LX system with Externe Laser Lift Off technology is an innovative solution that helps improve productivity and reduce environmental impact. TEL will continue to develop and introduce advanced technologies and products that meet the needs of our customers."

https://www.tel.com/news/product/2024/20241209 001.html

Investor Relations / February 26, 2025

- Equipment released in December 2024

- Incorporating extreme laser lift-off (XLO) technology

- Advanced thinning and critical technology for post-wafer bonding process

- Unique laser technology enables separation of the Si-substrate from the device layer

#### Advantages for process and environment

- · Enhanced efficiency in silicon active areas

- Fewer process steps required

- Reduced need for DI water usage and CO<sub>2</sub> emission

- Opportunity for wafer reuse

Si wafer B

Si wafer A

Device laver B

Device laver A

#### Ulucus<sup>™</sup> LX Advantages

Investor Relations / February 26, 2025

Confidential

### Video

### Today's Message

- TEL is accelerating the development of equipment for the bonding process, with the arrival of the 3D integration era.

- TEL is proactively developing fusion and Cu hybrid bonding technologies necessary for next-generation device manufacturing, leading the industry.

- TEL will further strengthen our engagement with key customers in memory and logic device manufacturing to expand the application of bonding technologies and achieve mass production implementation.