#### Tokyo Electron IR Day

January 20, 2021

#### **Forward Looking Statements**

#### Disclaimer regarding forward-looking statements

Forward-looking statements with respect to TEL's business plan, prospects and other such information are based on information available at the time of publication. Actual performance and results may differ significantly from the business plan described here due to changes in various external and internal factors, including the economic situation, semiconductor/FPD market conditions, intensification of sales competition, safety and product quality management, intellectual property-related risks, and impacts from COVID-19.

#### Processing of numbers

For the amount listed, because fractions are rounded down, there may be the cases where the total for certain account titles does not correspond to the sum of the respective figures for account titles. Percentages are calculated using full amounts, before rounding.

#### Exchange risk

In principle, export sales of Tokyo Electron's mainstay semiconductor and FPD production equipment are denominated in yen. While some settlements are denominated in dollars, exchange risk is hedged as forward exchange contracts are made individually at the time of booking. Accordingly, the effect of exchange rates on profits is negligible.

FPD: Flat panel display

#### Agenda

#### 1. Opening

#### 2. Presentation

- Aiming to Enhance the Corporate Value over the Medium to Long Term

- Supercritical Drying Technology in the Cleaning Process for Leading-edge Devices

- New Platform for the Etch Systems to Enhance Productivity

- Latest Single Wafer Deposition Processes and Development Activities for the Future

- TEL's Strategies toward Digital Transformation

#### 3. Q&A

16:35

17:15

15:35

15:30

# Aiming to Enhance the Corporate Value over the Medium to Long Term

January 20, 2021

Toshiki Kawai Representative Director, President & CEO

**First and Foremost**

## We want to express our deepest sympathies to all those who have been affected by COVID-19 or other natural disasters over the past year

**A Year of Steady Progress**

## TEL's business made steady progress Reaffirmed TEL's driving forces globally Honored the TEL Values and shared them with employees

Pride · Challenge · Ownership · Teamwork · Awareness

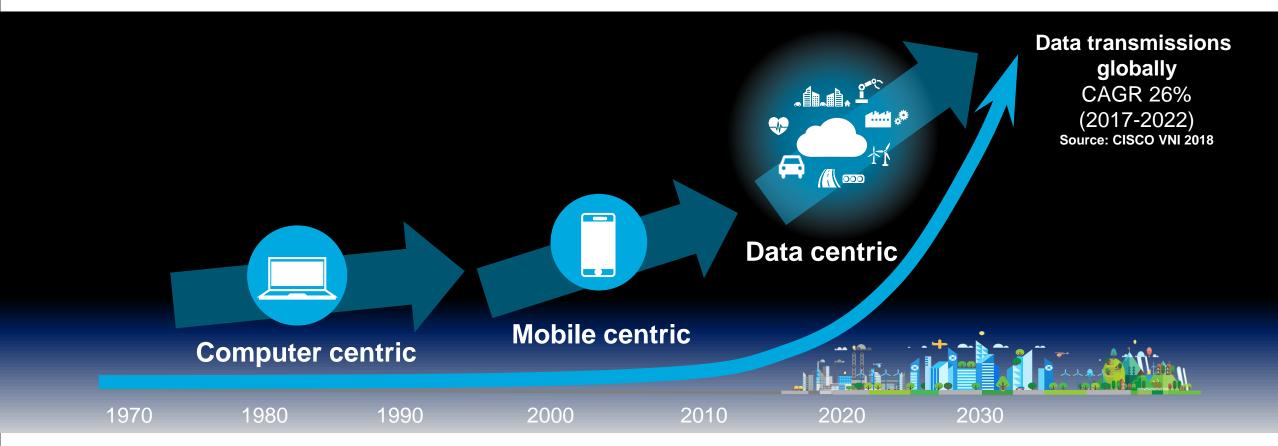

## **Beginning of Big Data Era**

A phase of higher growth with this data-centric era "Big years" ahead toward a future shift from selling products CORPIR/January 20, 2021 to selling value

## **Changes in Society Occurring Amid COVID Crisis**

# ICT\* being implemented widely around the world to build a strong and agile society

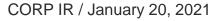

#### **WFE\* Market**

2021:

Increased demand for advanced semiconductors for hyperscale data centers and 5G smartphones will drive WFE market

Memory: Recovery in investment on liquidation of inventories Logic/Foundry: Continued stable and high level of investment

#### Last year's record WFE will continue into 2021 and beyond, leading to **Big Years**

## **Initiatives to Create New Value Toward Coming Big Years**

#### Tokyo Electron Technology Solutions (TTS) New production buildings began operation

Tohoku (lwate): Jul. 2020-

Yamanashi: Aug. 2020-

## Enhance production structure to swiftly prepare for future rise in demand

## **Initiatives to Create New Value Toward Coming Big Years**

TEL Digital Design Square (Sapporo): Began operation Nov. 2020

Miyagi Technology Innovation Center: Completion scheduled for Sep. 2021

# Meet needs for increasingly diverse extreme scaling technology

## **Initiatives to Create New Value Toward Coming Big Years**

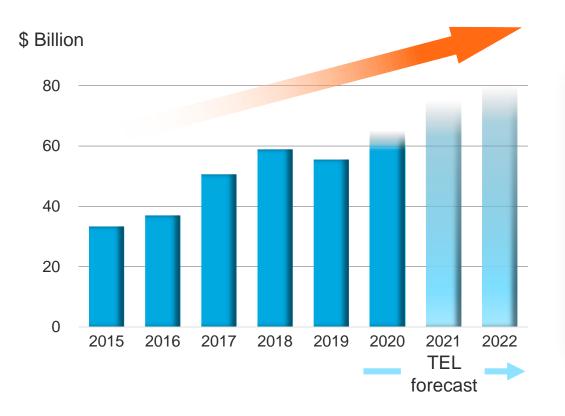

#### ¥400B in R&D investment in the three years from FY'20

Continue proactive R&D investment to achieve Medium-term Management Plan and maximize capture of growth potential for the future

## **Initiatives for the Environment**

## With our technology both support the development of ICT and reduce environmental burden

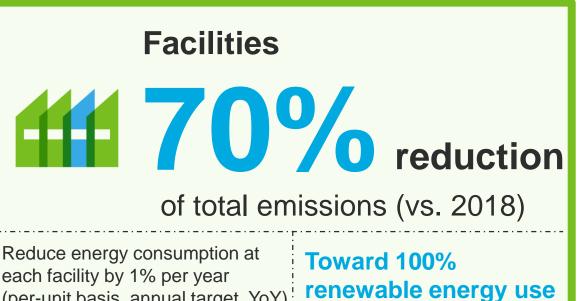

**Environmental Medium-term Targets for 2030 CO**<sub>2</sub> emissions reduction targets

Note: Of the total CO<sub>2</sub> emissions from TEL's value chain, approx. 87% are generated during product use

Long-term goal (2050)

As a leading corporation in environmental management, Tokyo Electron works actively to conserve the global environment. We strive to contribute to the development of a dream-inspiring society by proactively promoting the reduction of the environmental burden of both our products and facilities, and at the same time, providing evolutionary manufacturing technologies that effectively reduce the power consumption of electronic products.

(per-unit basis, annual target, YoY)

#### Support the development of a sustainable society through proactive initiatives for environmental issues CORP IR / January 20, 2021

## As a SPE and FPD equipment maker

Corporate Philosophy We strive to contribute to the development of a dream-inspiring society through our leading-edge technologies and reliable service and support.

## Supercritical Drying Technology in the Cleaning Process for Leading-edge Devices

January 20, 2021

Keiichi Akiyama VP & General Manager, CTSPS BU

#### Release of New Product with Supercritical Drying Technology

#### TEL Announces the Launch of CELLESTA™ SCD, a Single Wafer Cleaning System

Tokyo Electron (TEL) announced today the launch of the CELLESTA™ SCD single wafer cleaning system, scheduled for release in January 2021.

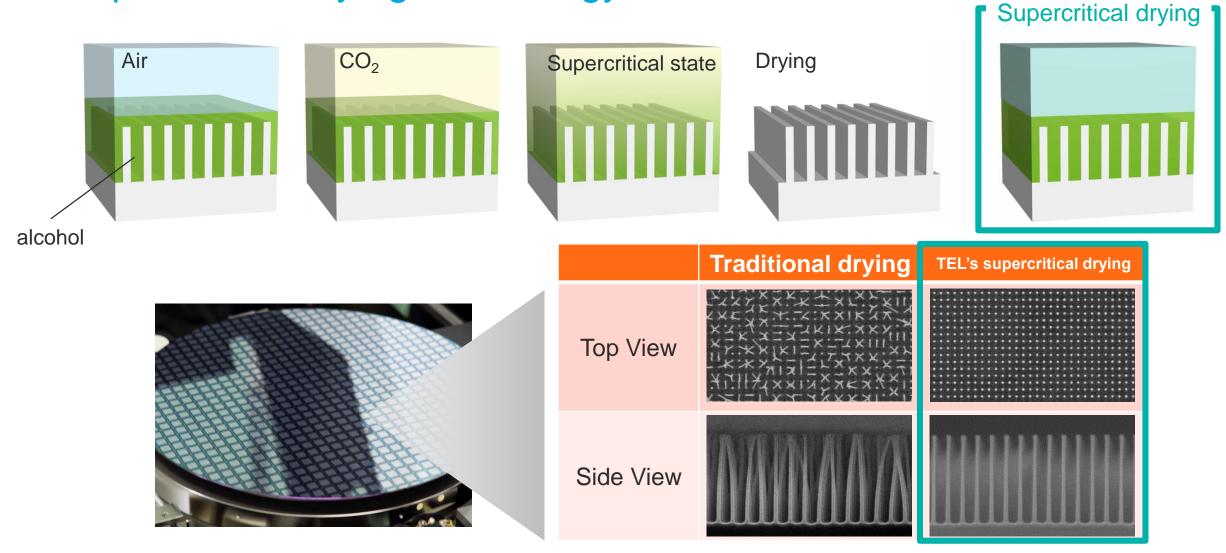

TEL's CELLESTA series of products are widely used for cleaning silicon wafers in the semiconductor manufacturing process. The soon-to-be-released CELLESTA SCD integrates a dedicated supercritical drying chamber on the mass production-proven CELLESTA platform.

In wafer cleaning, it has been customary to employ low surface tension alcohol solutions in the drying process. However, due to continued semiconductor scaling and adoption of multi-layer structures in highly advanced devices, pattern collapse in the drying process has become one major issue. In response, TEL has developed a pattern collapse-free drying method that uses a supercritical fluid, bringing the technology to the market as equipment for mass production.

With the addition of CELLESTA SCD and its dramatically improved cleaning and drying technologies to the existing line of single wafer cleaning systems, TEL is meeting advanced technological needs in semiconductor manufacturing to drive further growth of the semiconductor industry.

"CELLESTA SCD offers an innovative technological solution to the wafer-drying challenges in the post cleaning process for manufacturing advanced semiconductor devices," said Keiichi Akiyama, Vice President & General Manager, CTSPS BU at TEL. "We will continue to leverage our ability to develop innovative technologies and deliver high value-added products, providing optimum solutions for technological issues associated with the most advanced semiconductor devices."

TEL will be showcasing CELLESTA SCD at SEMICON Japan 2020 Virtual. Please visit our virtual booth during the show. Period:  $2020/12/11 \sim 2021/1/15$

CELLESTA is a registered trademark or trademark of Tokyo Electron Group in Japan and/or other countries.

CELLESTA<sup>™</sup> SCD SCD: Supercritical dry

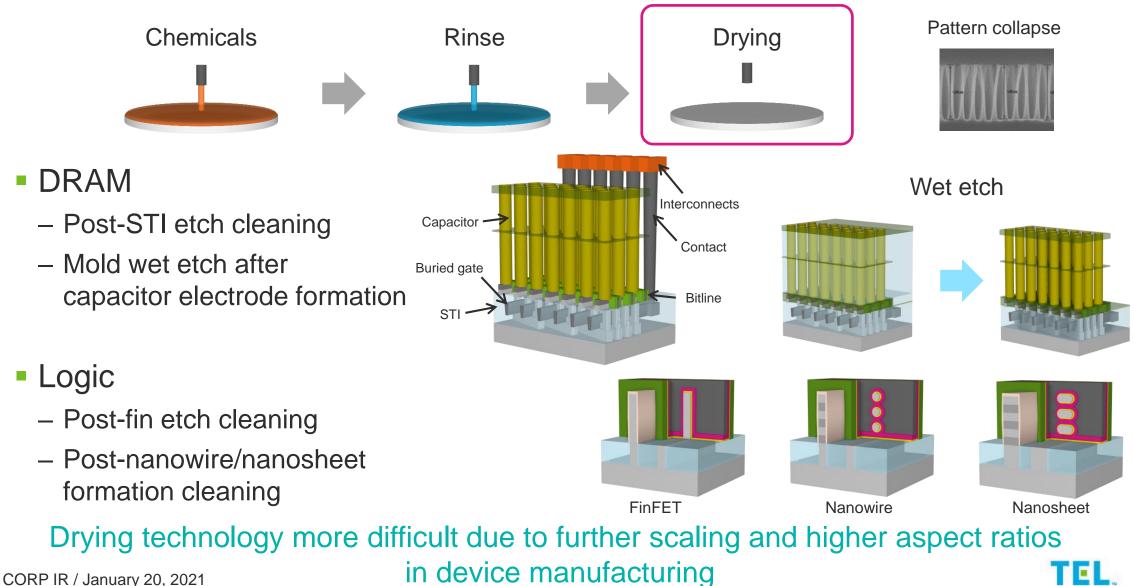

#### **Cleaning Process in Semiconductor Manufacturing**

Post-etch cleaning

Cleaning chamber's state

Contact etch

Slit etch

#### General cleaning process

#### Cleaning by chemicals

Rinse

Drying

## Technology Challenges in Cleaning for State-of-the-Art Devices

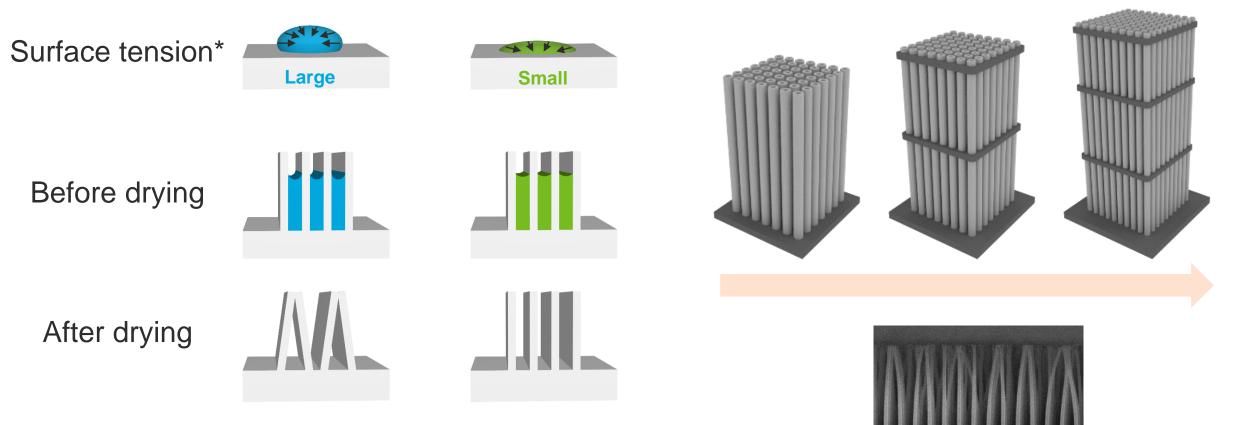

#### Pattern Collapse Mechanism and Solution

\*Surface tension: The tendency of a liquid or solid to reduce its surface area

As aspect ratios have become higher, the collapse prevention approach of chemical replacement for lowering surface tension, surface modification, etc., is reaching its limit

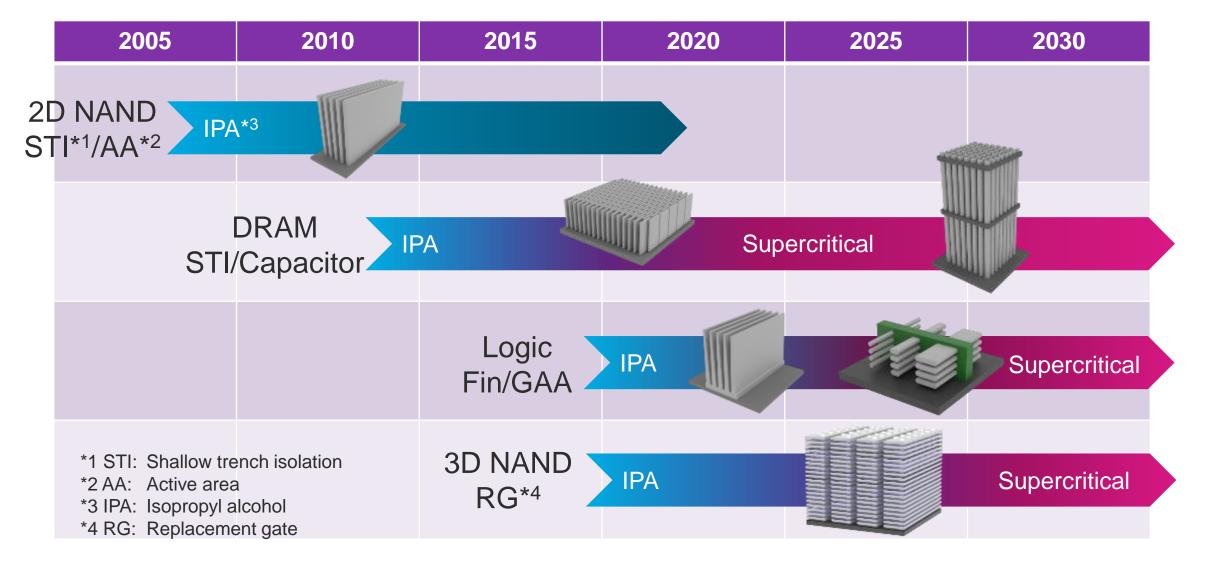

#### Next Generation Drying Technology

- The next generation drying technologies are supercritical dry and sublimation dry

- As supercritical dry is the most effective solution for the issues in drying technology, TEL has released the CELLESTA<sup>™</sup> SCD for mass production

- Supercritical dry is expected to be used in a wide range of applications, including for complex structures like capacitor electrodes and fragile films like PCRAM memory cells

|                   | Application                                                  | Residue     | Oxidation/material loss |

|-------------------|--------------------------------------------------------------|-------------|-------------------------|

| Supercritical dry | Usable for complex<br>and/or high aspect ratio<br>structures | Very little | No                      |

| Sublimation dry   | Not suitable for stacked<br>or fragile structures            | Significant | Yes                     |

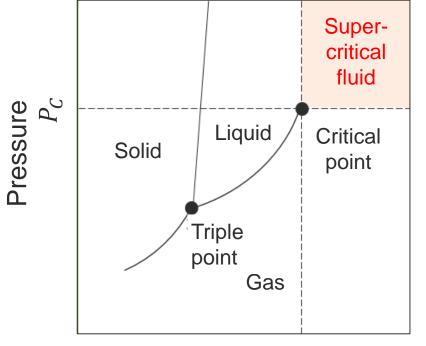

#### Supercritical Drying Technology

- What is supercritical?

- The state where temperature and pressure are above their critical point

- Holds properties between those of liquid and gas

- Surface tension is zero

- Challenges for introducing in semiconductor production process

- Stable operation at pressure regions hitherto unused

- Particle control at the nano-level

Effective against pattern collapse because surface tension is theoretically zero Particle control is required at the nano-level for leading-edge processes

*T<sub>C</sub>* Temperature

### Supercritical Drying Technology

Supercritical drying technology prevents pattern collapse

#### Drying Technology Roadmap

#### Summary

- TEL is proposing supercritical drying technology for pattern collapse, a technological issue in wafer cleaning

- We will continue to offer new technologies and solutions to various technological issues in wafer cleaning for leading-edge devices as a partner of semiconductor manufacturers

#### New Platform for the Etch Systems to Enhance Productivity

January 20, 2021

Isamu Wakui VP & General Manager, ES BU

#### **Business Opportunities and Basic Strategy**

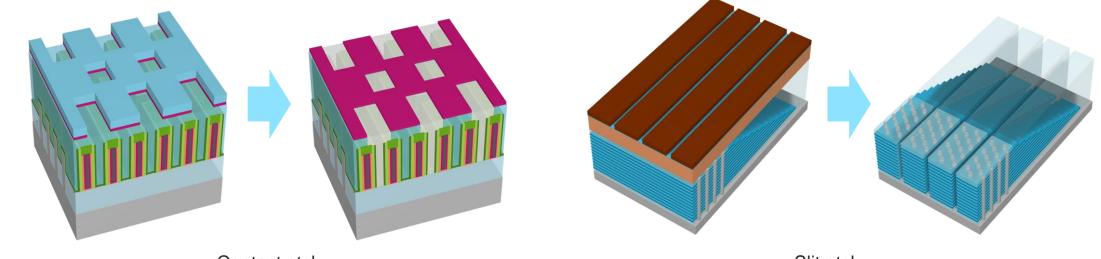

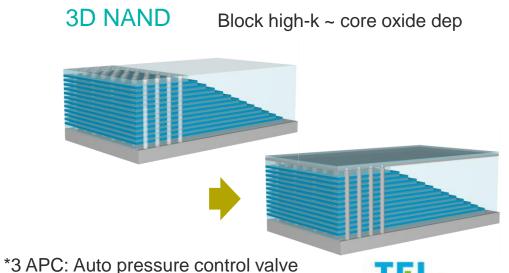

- Continued high level of investment expected in the etch systems market driven by 3D NAND and patterning

- Focus on HARC, patterning and interconnects, which leverage TEL's strengths Aiming to raise share and profitability

Continuing proactive investment toward further market growth in future

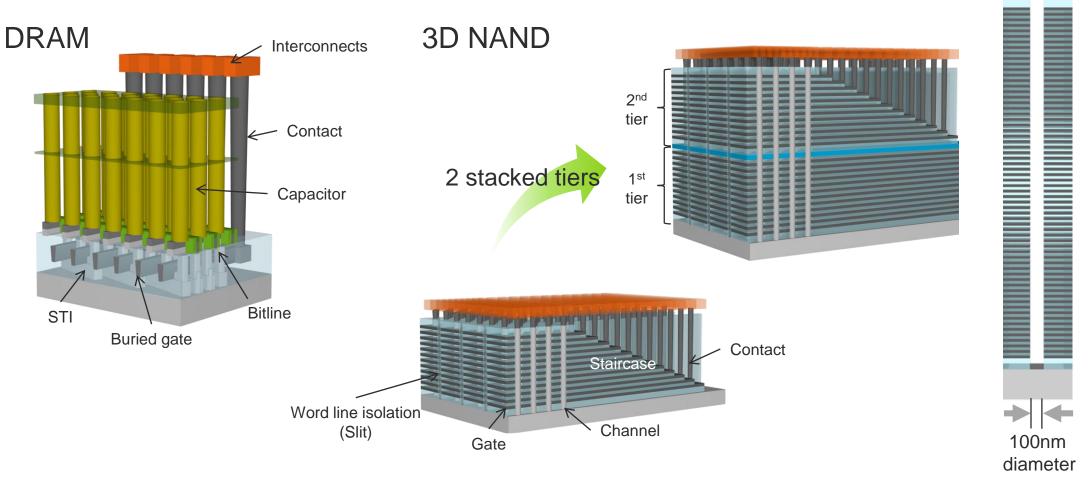

#### **Challenges in Etch for Memory**

Aspect ratio = 50-70:1

As the number of layers and aspect ratio increase, it is necessary to balance processing performance and productivity

#### Challenges of Etch for Logic

#### Flexible equipment layout sought for diversified etch processes

CORP IR / January 20, 2021

\*1 PDN: Power delivery network

\*2 SAQP: Self-aligned quadruple patterning

\*3 SAC: Self-aligned contact

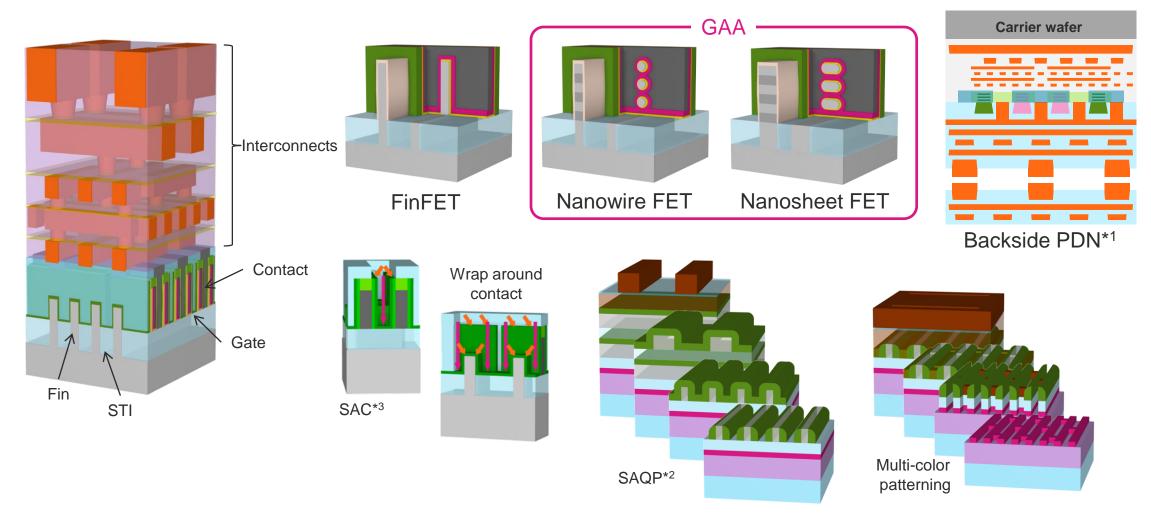

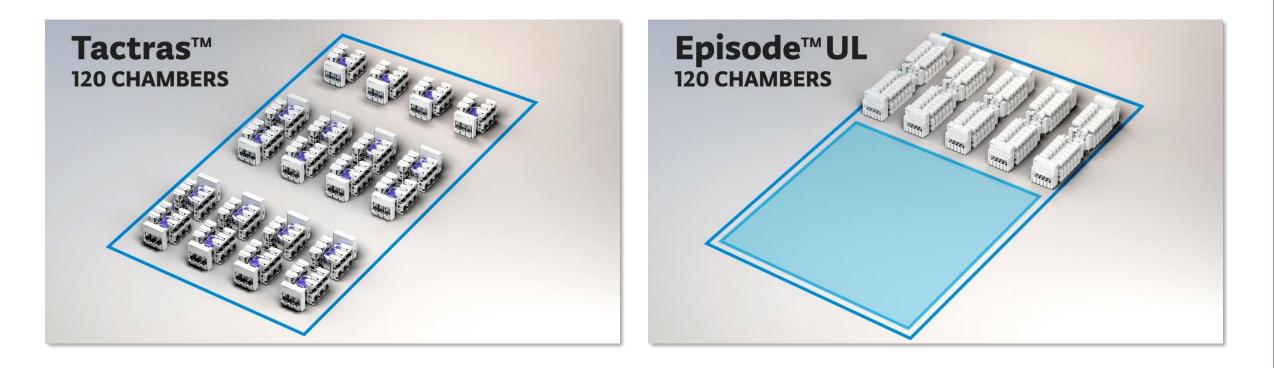

### History of TEL Etch Systems

**TE5000** TEL's first original dry etch tool

**TE8500**

**UNITY™ II** TEL's first platform with multi-chambers

Tactras<sup>™</sup> BX Realized 8 chambers in one system

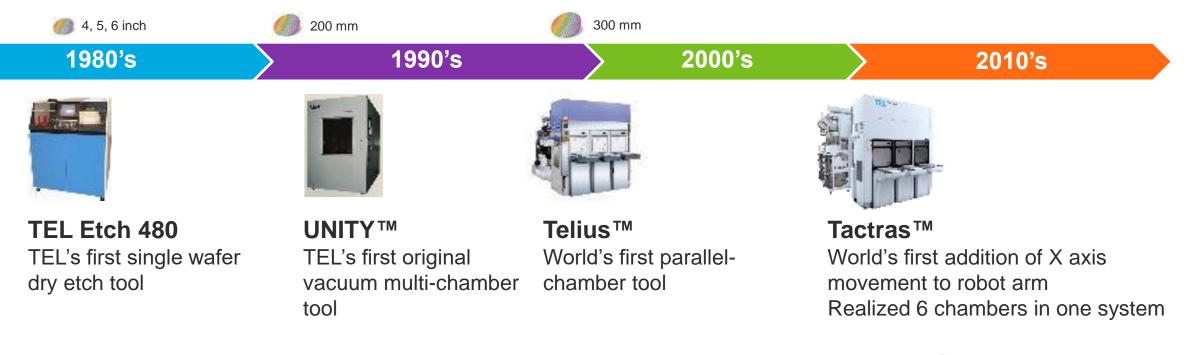

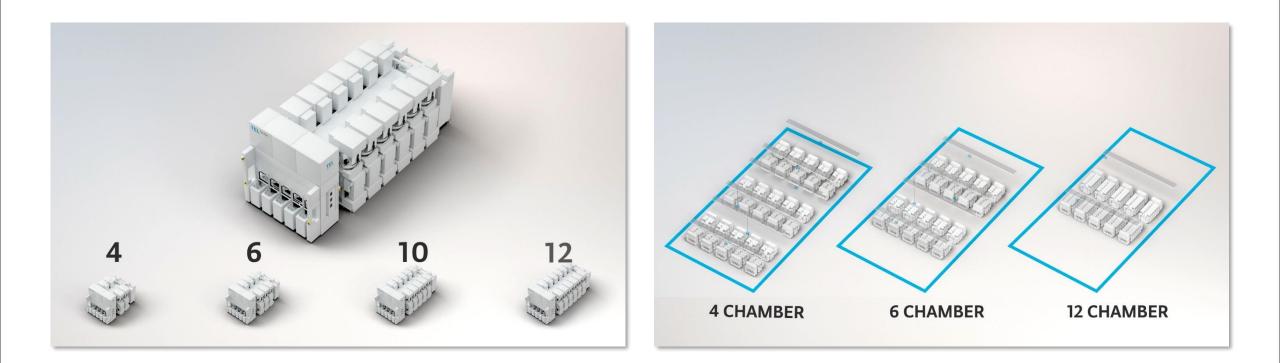

#### Episode<sup>™</sup> UL Features

Flexible layout available to accommodate needs Improved productivity through space saving and smart tools

#### Episode<sup>™</sup> UL: Layout

#### Select from 4 options 4, 6, 10, and 12 chamber designs

Flexible layout available to accommodate fab space and target processes

#### Episode<sup>™</sup> UL: Space

Significantly reduced footprint per chamber

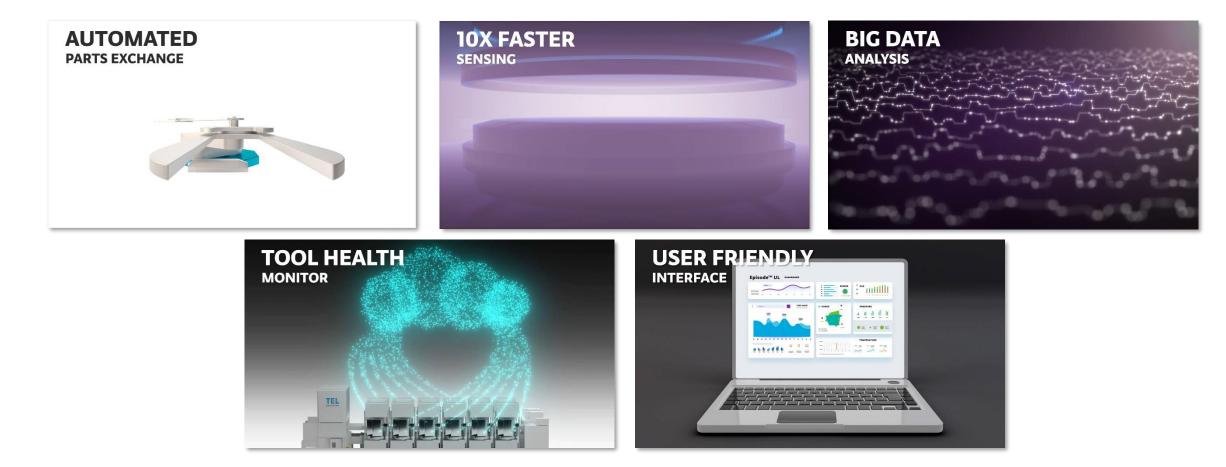

#### Episode<sup>™</sup> UL: Smart Tools

Includes automated parts exchange functions, multiple sensors and a high-speed control system Autonomous process control possible through big data analysis using TEL's own smart tools

CORP IR / January 20, 2021

## Episode<sup>™</sup> UL Movie

#### Summary

- Flexible layout:

- Capable of selecting any number of chambers, from 4 to 12

Space:

- Significantly reduced footprint per chamber

- Smart Tools:

- Includes automated parts exchange functions, multiple sensors and a high-speed control system

Autonomous process control possible through big data analysis using TEL's own smart tools

### Latest Single Wafer Deposition Processes and Development Activities for the Future

January 20, 2021

Hiroshi Ishida VP & General Manager, TFF BU

### **Thin Film Formation Product Lineup**

# **Oxidation / CVD / ALD / PVD**

#### **Batch Process\***

Process:Oxidation/CVD/ALDReaction:Thermal/PlasmaMaterial:SiO2/Si3N4/High-k/MetalFeature:100 to 150 wafers/batch

#### Semi-batch Process

Process: ALD Reaction: Thermal/Plasma Material: SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/High-k Feature: 5 to 6 wafers/batch

#### Single Wafer Process

| Process:  | CVD                        |  |

|-----------|----------------------------|--|

| Reaction: | Thermal/Plasma             |  |

| Material: | Metal/High-k/Ferroelectric |  |

| Feature:  | Superior step coverage     |  |

#### Process: PVD Reaction: Thermal/Plasma Material: Magnetic material/Metal Feature: Multi-film stacking

\* Installed base >10,000 @ 300mm

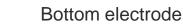

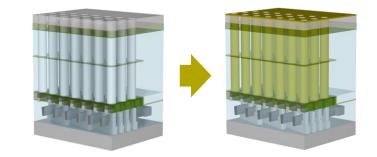

# Trias*e*<sup>+™</sup> EX-II<sup>™</sup> Advance: TiN for Super High Aspect Ratio

- Features

- State-of-the-art advanced sequential flow deposition (TiN)

- High precursor and gas supply provides superior step coverage ratio for the most advanced memory devices

- Thin film continuity (Continuous film at <10 Å)

- Excellent thickness uniformity ( $1\sigma < 1\%$ )

- Wide temperature capability (400 to 600°C)

- High speed pressure control enables higher productivity

- Applications

- DRAM capacitor electrode

- 3D NAND word line barrier

- Other high surface area structures

DRAM

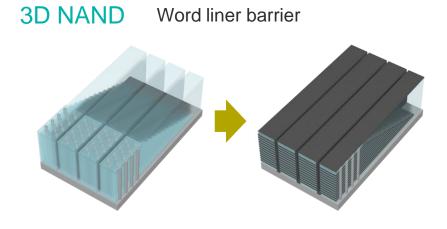

# Trias*e*<sup>+™</sup> EX-II<sup>™</sup> HK: High Quality High-k Dielectric

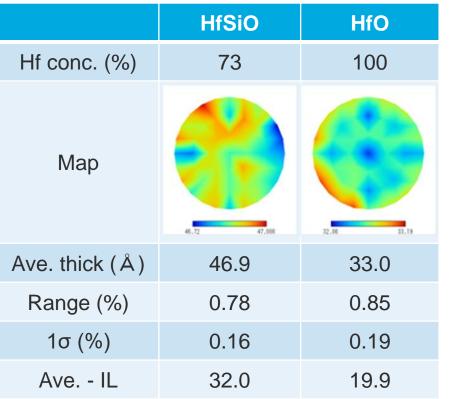

Features

- Designed for HfO process @ ~400°C and ultra low carbon (~1E19 atoms/cm<sup>3</sup>)

- Liquid Hf precursor with DLI\*<sup>1</sup> vaporizer unit enables ideal ASFD\*<sup>2</sup> process with high Hf flow

- Unique gas insertion enables non-uniformity of < 1% within wafer</li>

- Enhanced exhaust line with high-speed APC\*<sup>3</sup> and 100A piping for longer wet PM\*<sup>4</sup> cycle

- Applications

- DRAM peripheral high-k metal gates

- 3D NAND block high-k dielectric

\*1 DLI: Direct liquid injection \*3 APC: Auto pressure control valves \*2 ASFD: Advanced sequential flow deposition \*4 PM: Preventative maintenance

High-k dielectric

40

# Triase<sup>+™</sup> EX-II<sup>™</sup> HK: High Quality High-k Dielectric

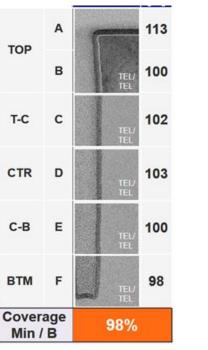

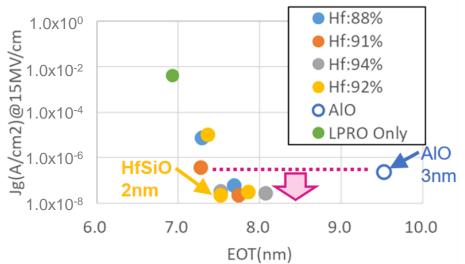

#### Uniformity

#### Coverage

Hole aspect ratio = 55:1

Leak current

Leak current of HfSiO 2nm-thick is smaller than that of AIO 3nm-thick on TEL MOS capacitor

#### Enables high-k thin film formation on high aspect ratio structures

# Triase<sup>+™</sup> EX-II<sup>™</sup> MS: Multi-source Supply for Controllable Film Composition

#### Under development

#### Features

- New Chamber design for multi-source supply

- Capable of composition ratio control

### Applications

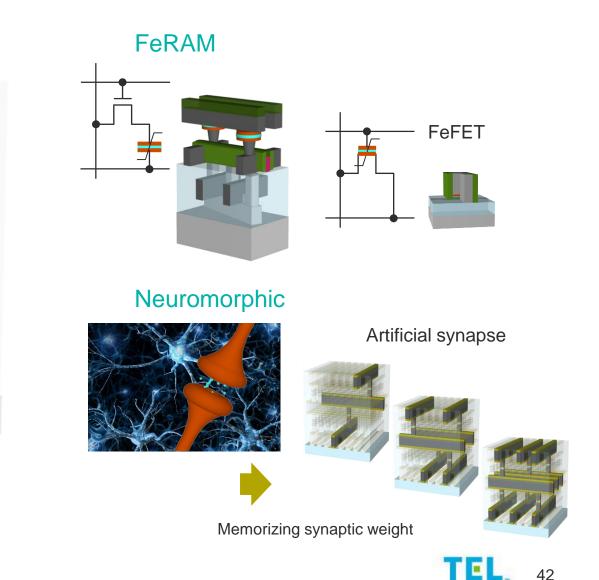

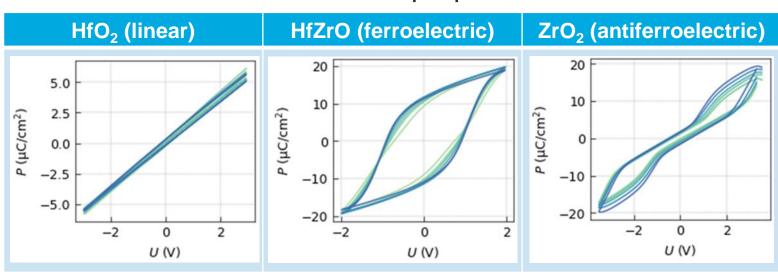

- Ferroelectric FET for non-volatile memory

- Extension to storage class memory

- Extension to neuromorphic devices (memorizing synaptic weight)

# Triase<sup>+™</sup> EX-II<sup>™</sup> MS: Multi-source Supply for Controllable Film Composition

#### Under development

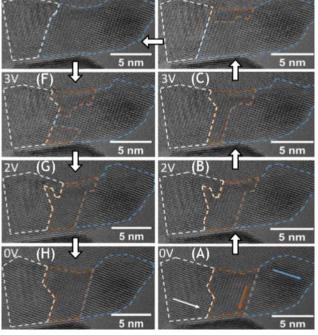

#### Ferroelectric properties

Multi-source supply enables controllable film composition, making possible the formation of various functional films In-situ TEM measurement with simultaneous voltage cycling of antiferroelectric ZrO. Crystal grains grow and shrink by field driven domain wall migration as the voltage cycles from  $0V \rightarrow 4V \rightarrow 0V$ .

Demonstrated at TEL Technology Center, America.

Reference: Lombardo et al., VLSI 2020

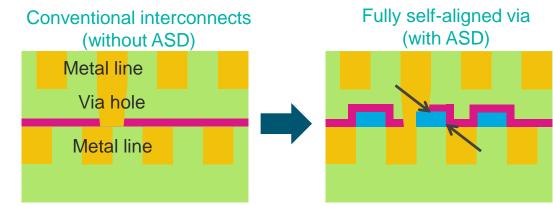

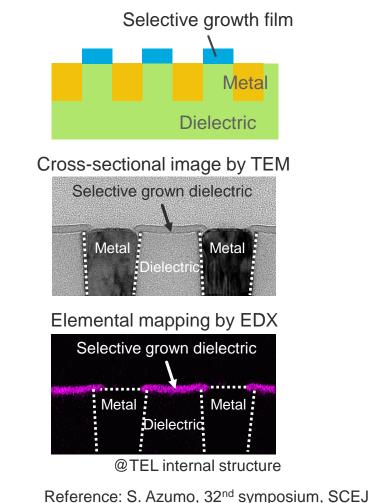

# New Opportunity: Area Selective Deposition for Sustainable Scaling

#### Features

- Selective growth of film on metal/dielectric surface

- Excellent surface pre-treatment technology for high selectivity between growth and non growth surfaces

- Applications

- Logic BEOL, Fully Self-Aligned Via (FSAV)

- To every scaled patterning for enhancing lithography misalignment margin

#### Area selective deposition (ASD)

CORP IR / January 20, 2021

# Summary

- TiN for super high aspect ratio

- Sustains DRAM capacitor scaling

- Enhances word line performance in 3D NAND

- High quality high-k dielectric

- Newly adopted for DRAM peripheral high-k metal gates

- Enhances control gate performance in 3D NAND

- Multi-source supply

- Realizes controllability of film composition

- Area selective deposition

- Enlarges misalignment margins in patterning

# TEL's Strategies toward Digital Transformation

January 20, 2021

Noritaka Yokomori Deputy General Manager, Corporate Innovation Division

### **TEL's Vision for Digital Transformation**

Industry as a whole is increasingly adopting digital transformation (DX), and the semiconductor industry is no exception. DX occupies an important position as one piece of the solution to demand for further scaling and multi-layering

Cloud services

AR/VR

# **TEL DX Vision**

A global company where all employees drive enterprise value creation sustainably through activities such as value addition and efficiency improvements by leveraging digital technology

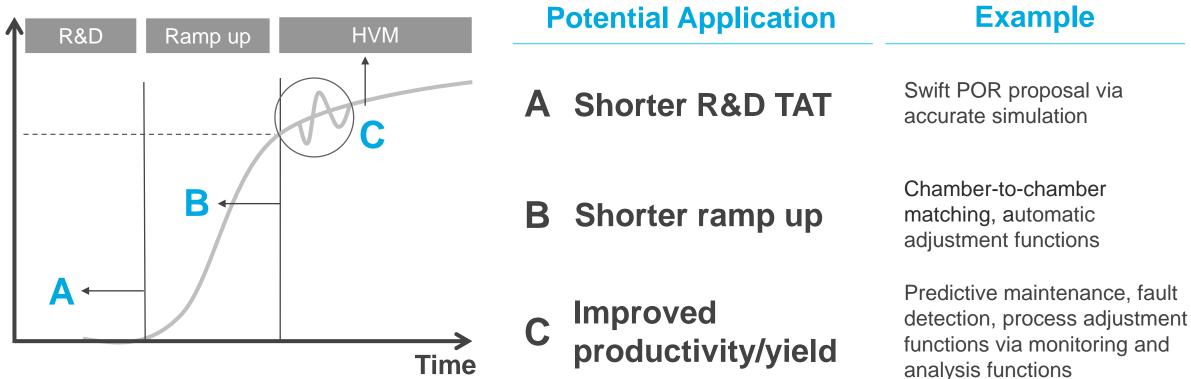

# DX in Contributing to Customers' Value Creation

#### Yield

From development to production, contributes to customers' value creation in a range of settings

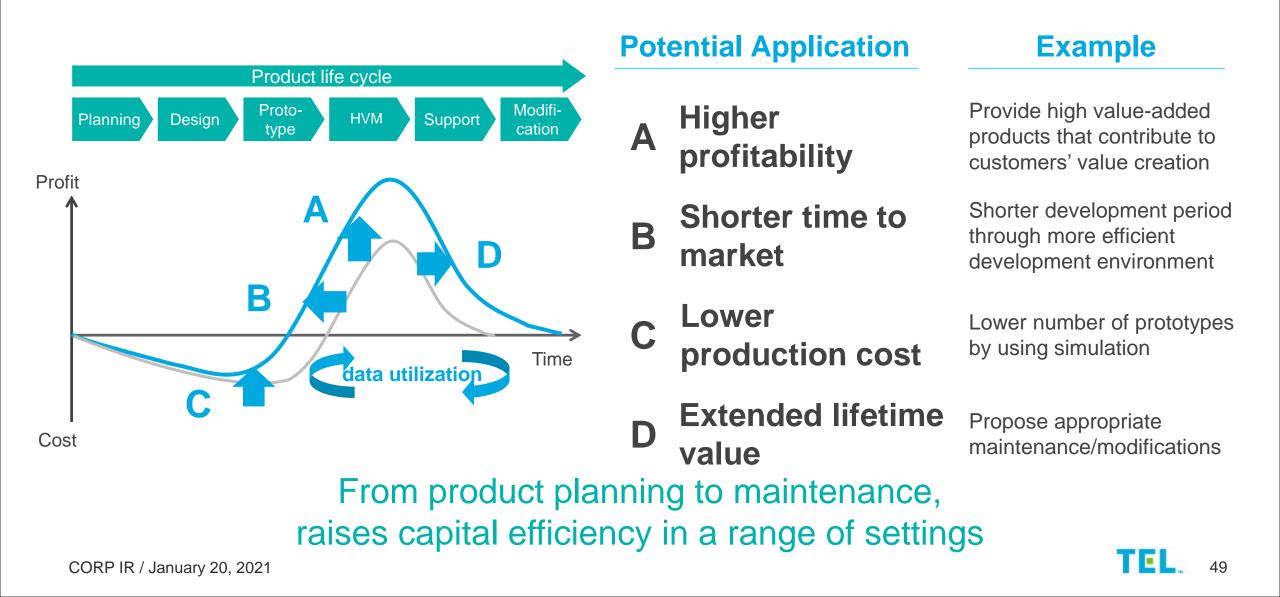

# DX in Raising Capital Efficiency

# **DX** Activities

#### **Digital enablers**

- High-performance computing

- Cloud infrastructure

- AI technology

- IoT, xR

#### Surrounding environment

- Progress in data sharing and collaboration in supply chains

- High expectations for AI and robot support of humans

Added value creation/improved capital efficiency

#### Achieving goals

Resolution of high value problems

#### High value problem

- Quality

- Cost

- Speed

- Productivity

- Energy consumption

### 2. Analysis and prediction

Analysis and prediction with digitalized data

### Digital transformation in resolving high value problems

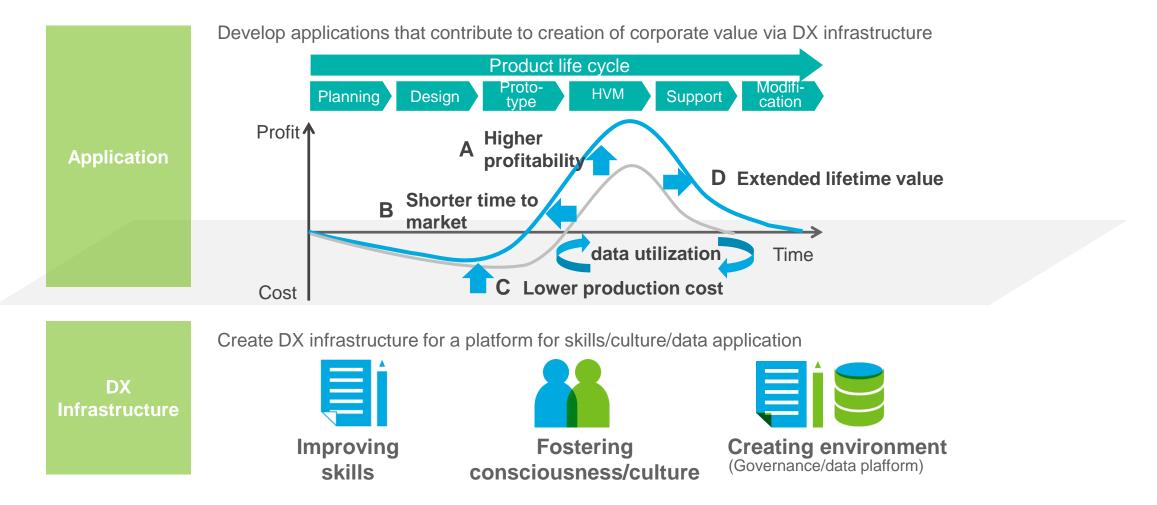

# **Overall Image of TEL's DX Project**

Utilize DX infrastructure to develop applications that create corporate value

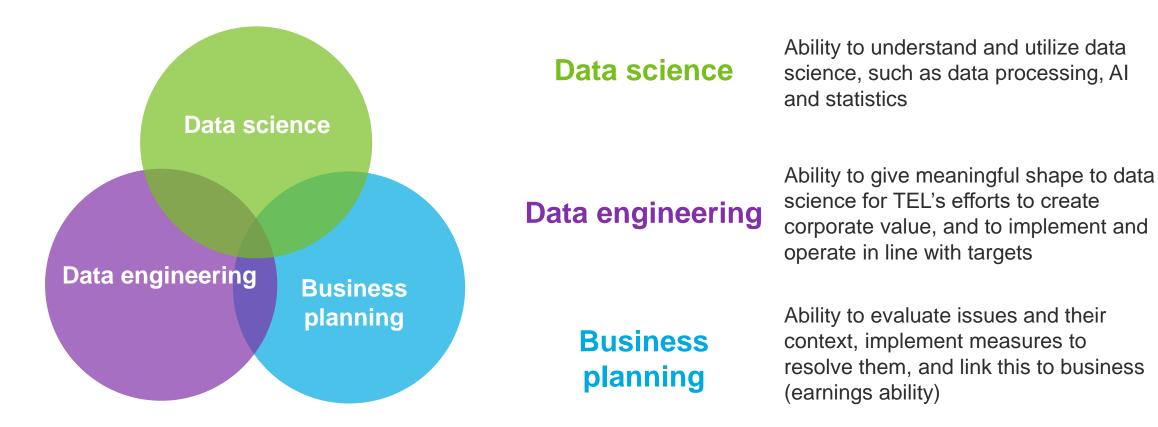

### **DX Engineer Training Plan**

Systematically train human resources to utilize data science in TEL's business

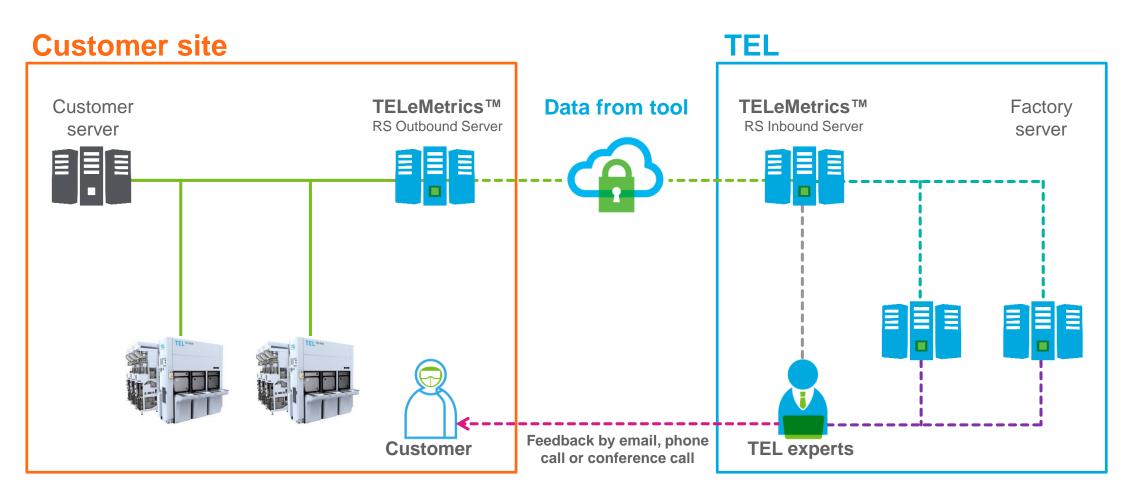

# TELeMetrics™: Remote Connection with Customer Fabs

#### Transformation from selling man-hours to selling value

CORP IR / January 20, 2021

### Remote Support Using AR

#### **Customer's cleanroom**

#### **TEL support center**

AR: "Augmented reality"; technology that can overlay information on a view of the real world via smart glasses

Apply new technology in this era of big data to enhance service efficiency

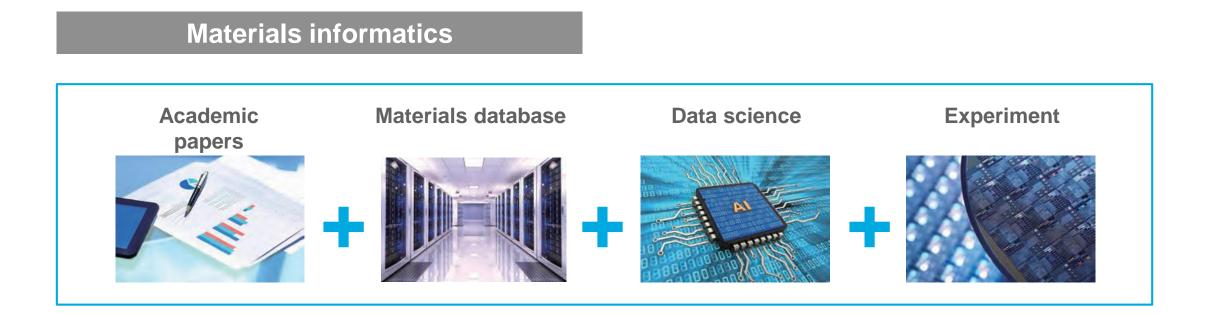

# **Exploring Materials Through AI**

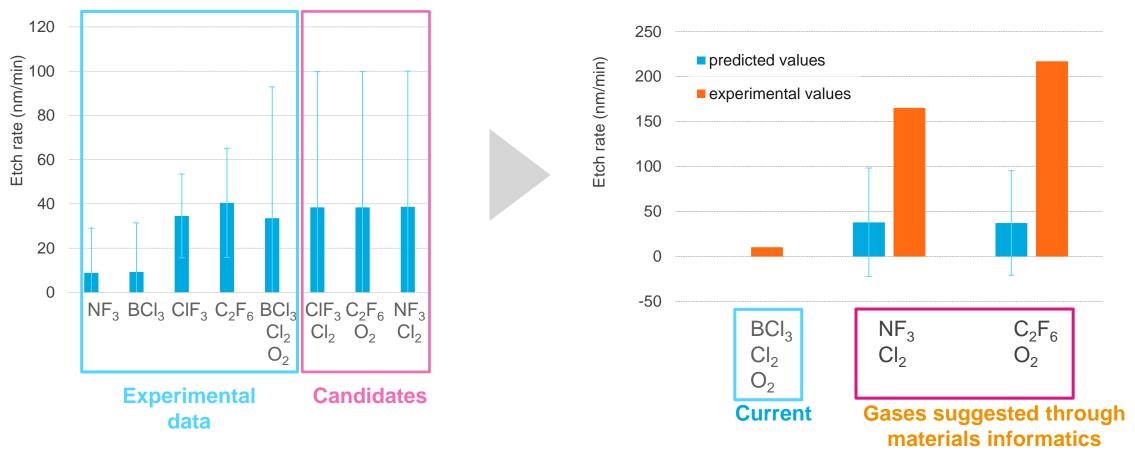

A way to co-optimize process requirements and materials

#### Explore materials for use in etching metal oxides

# **Comparison of Predicted and Experimental Values**

Gases with higher etch rates than before were suggested using machine learning

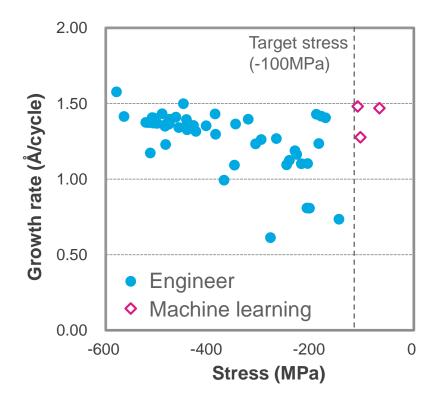

# **Process Optimization Through AI**

#### Plasma atomic layer deposition (PE-ALD) film stress adjustment

Process: PE-ALD SiO<sub>2</sub> deposition Target: film stress → between -100MPa 0MPa

- Previous method using engineers

- Unable to achieve target film stress levels

- Gathered test data, studied with AI

- Achieved target stress levels

### Machine learning demonstrated the capability of process optimization

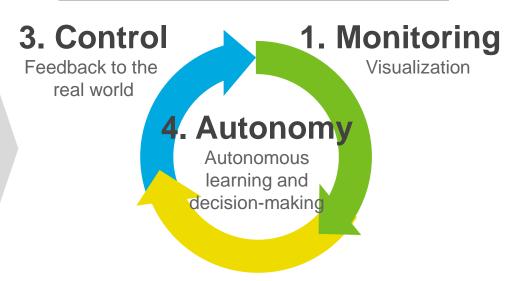

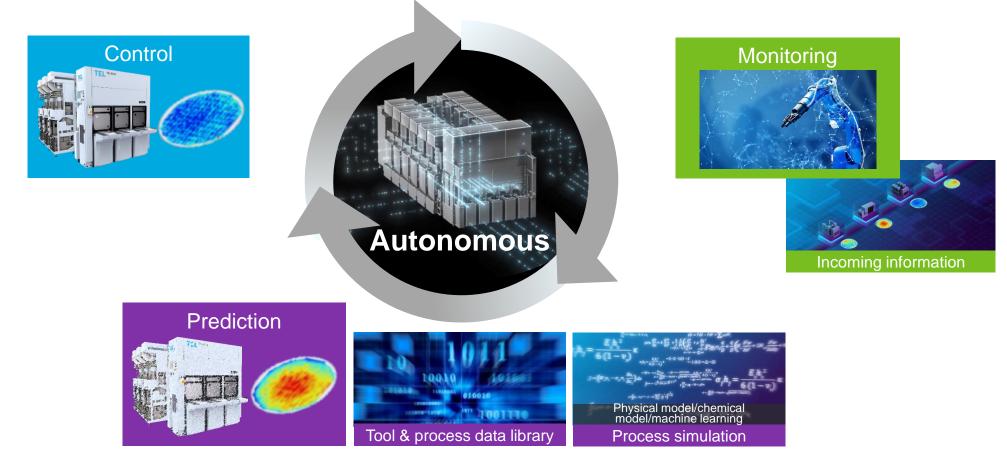

# Supporting Customer Value with Autonomous Equipment

Autonomous learning by gathering necessary information Equipment senses its environment and state to maintain optimal status

CORP IR / January 20, 2021

# **TEL Digital Design Square**

### **TEL DX Vision**

A global company where all employees drive the sustainable creation of enterprise value by leveraging digital technology in activities including adding value and raising efficiency

#### **Development activities**

Opened the TEL Digital Design Square as the home base for DX activities

CORP IR / January 20, 2021

# **TEL Digital Design Square Movie**