### Investors' Guide

August 4, 2025

Tokyo Electron Limited

## Contents

| 1.   | TEL Overview                                                                                                                                                                                 | 3                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.   | Semiconductor and SPE Market Outlook                                                                                                                                                         | 17                               |

| 3.   | Corporate Principles and New Medium-term Management Plan                                                                                                                                     | 26                               |

| 4.   | Business Environment and Financial Estimates                                                                                                                                                 | 34                               |

| 5.   | Sustainability                                                                                                                                                                               | 42                               |

| 6.   | Diversity of Semiconductor Technology ~Technology Roadmap~                                                                                                                                   | 54                               |

| 7.   | SPE New Equipment Initiatives 7-1 Frontend, Patterning Technologies 7-2 Frontend, Unit Process 7-2-1 Etch System 7-2-2 Deposition System 7-2-3 Cleaning System 7-3 Backend Business Strategy | 60<br>64<br>72<br>73<br>82<br>89 |

| 8.   | MAGIC Market and Field Solutions Business Initiatives                                                                                                                                        | 113                              |

| 9.   | Digital Transformation (DX) Initiatives                                                                                                                                                      | 120                              |

| 10.  | Procurement and Manufacturing Strategy                                                                                                                                                       | 135                              |

| Appe | 144                                                                                                                                                                                          |                                  |

## 1. TEL Overview

## **Company Profile**

**Established**

November 11, 1963

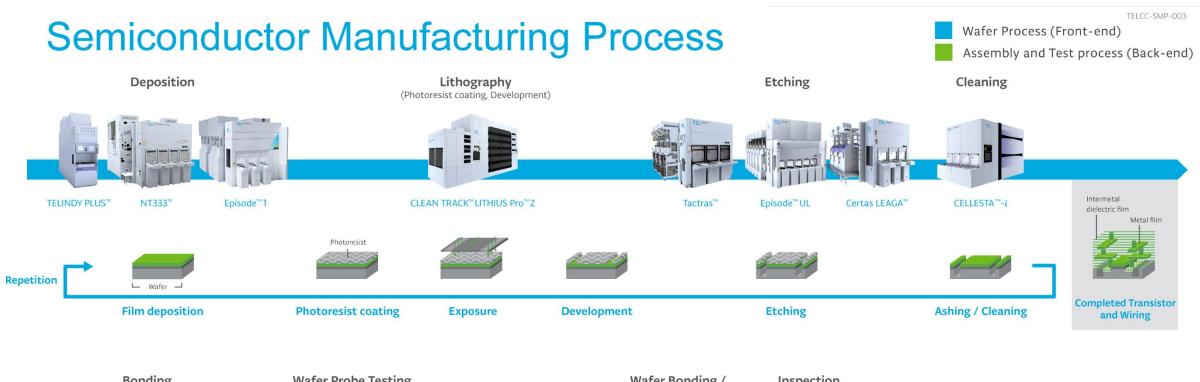

Major Products and Services

Semiconductor Production Equipment

Capital

54.9 Billion Yen

Sales/Profit

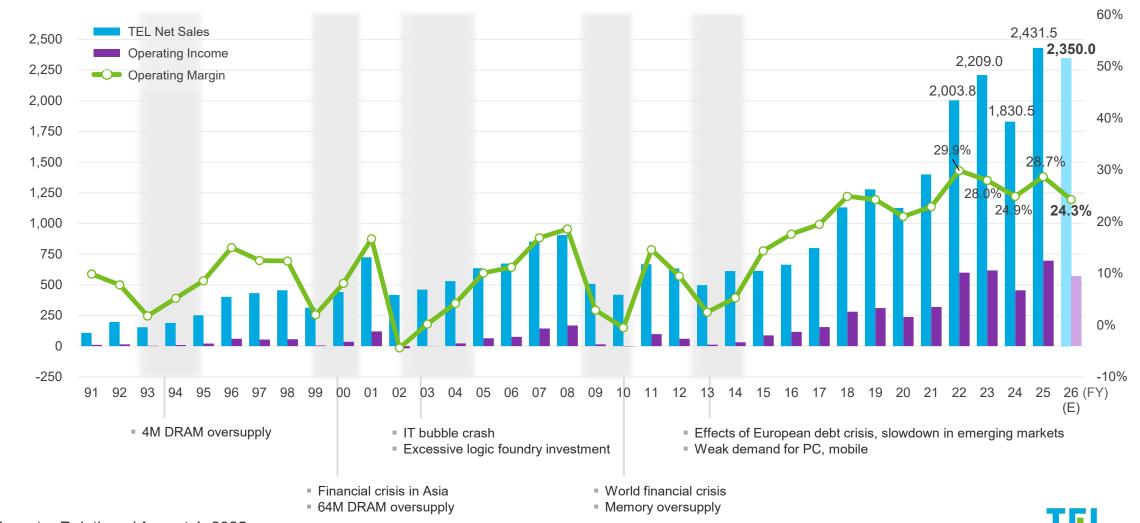

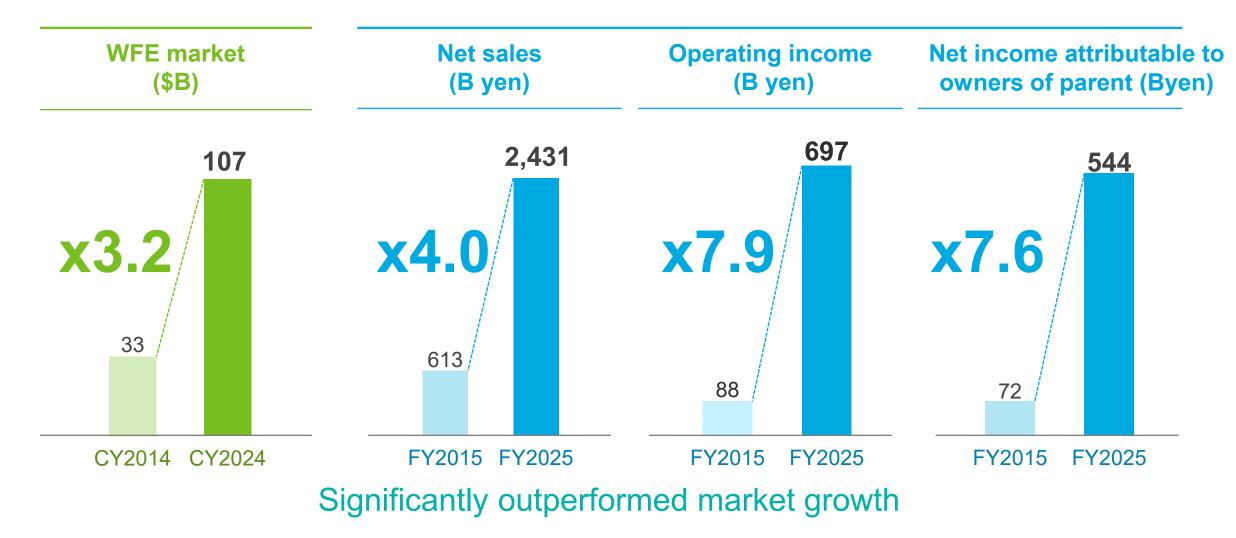

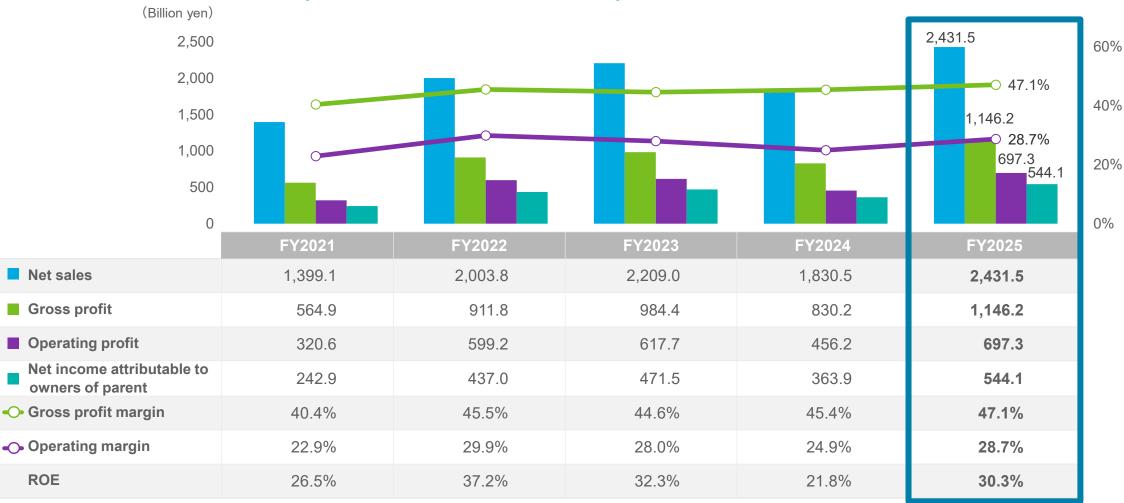

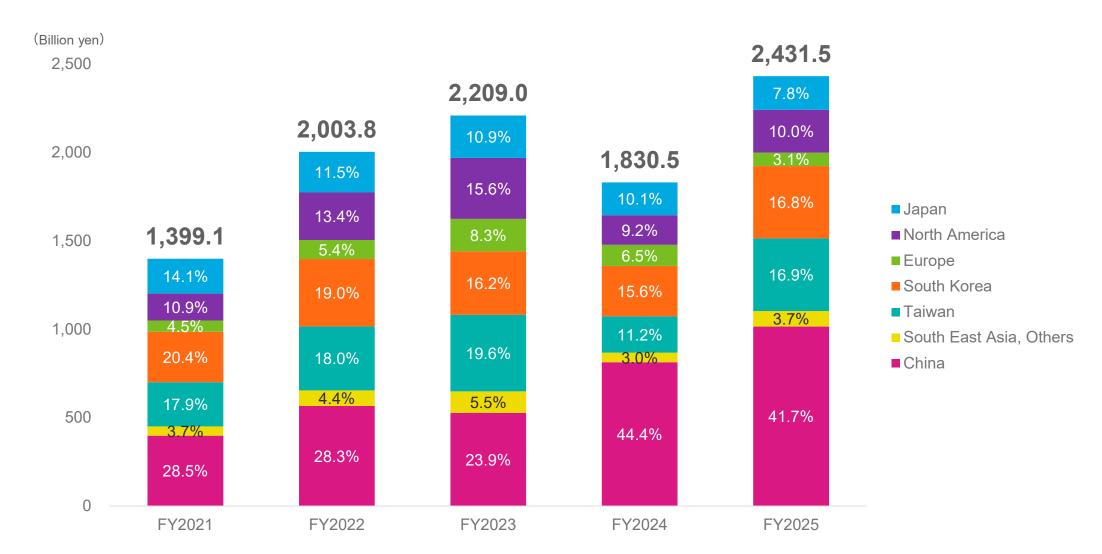

Net sales 2,431.5 Billion Yen / Operating income 697.3 Billion Yen / Operating margin 28.7% (Fiscal 2025)

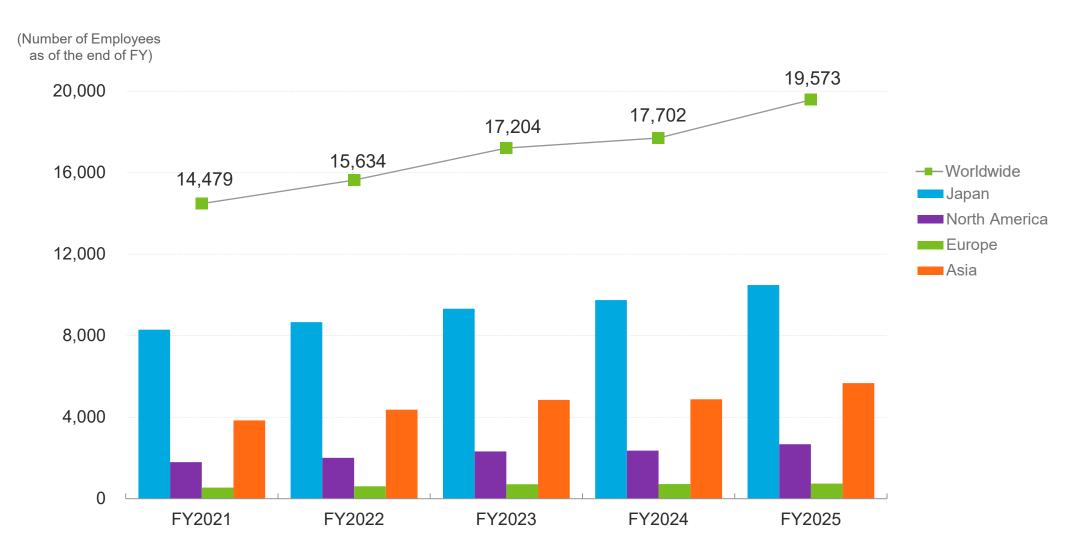

Number of Employees

2,347 (non-consolidated) 20,273 (consolidated)

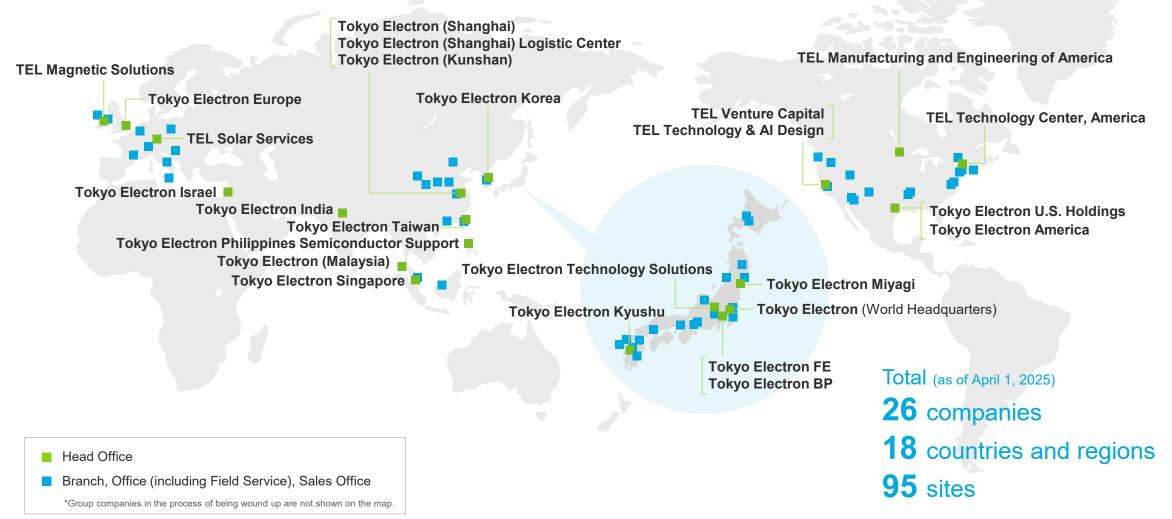

**Global Network**

Japan: 6 companies / 30 sites

Overseas: 20 companies / 17 countries and regions / 65 sites

Total: 26 companies / 18 countries and regions / 95 sites (consolidated)

(as of April 1, 2025)

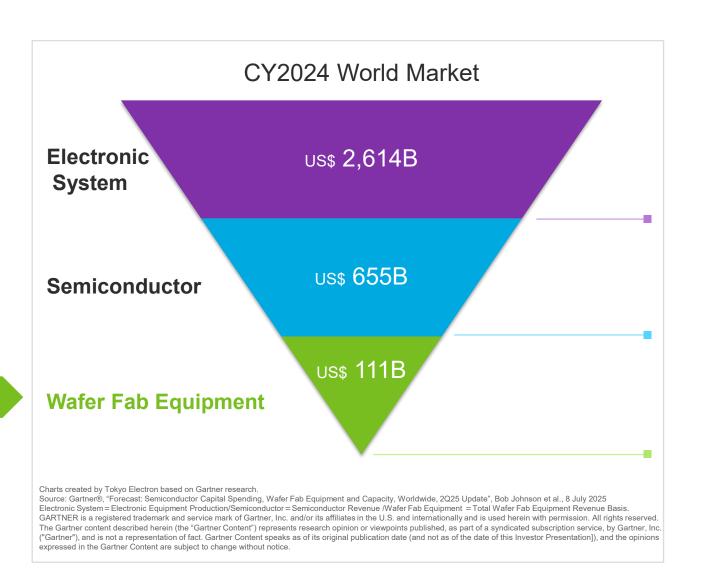

## The Market TEL Participates in

The market TEL

participates in

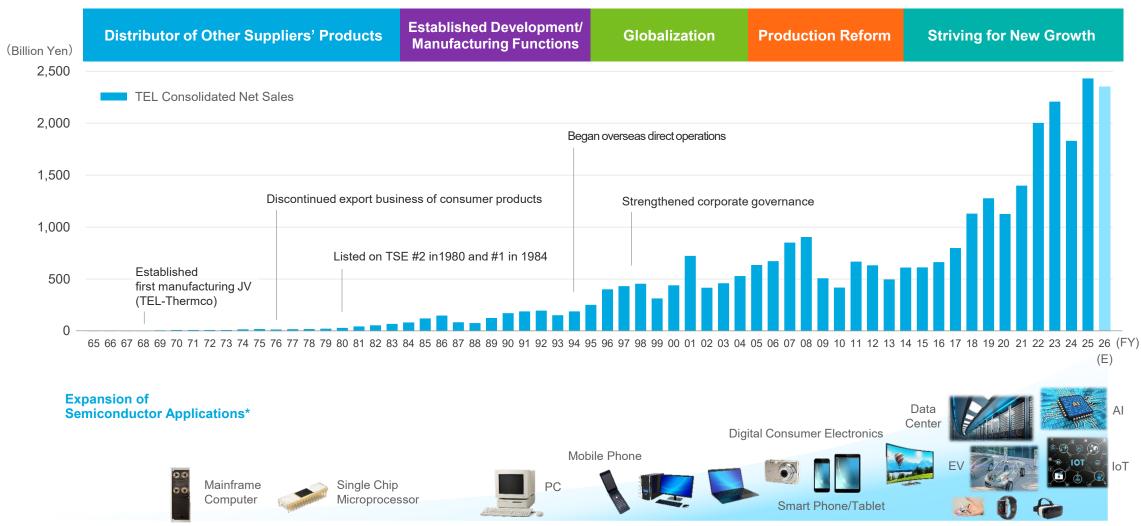

### TEL's Growth

## Financial Performance: Sales and Operating Margin

(Billion Yen)

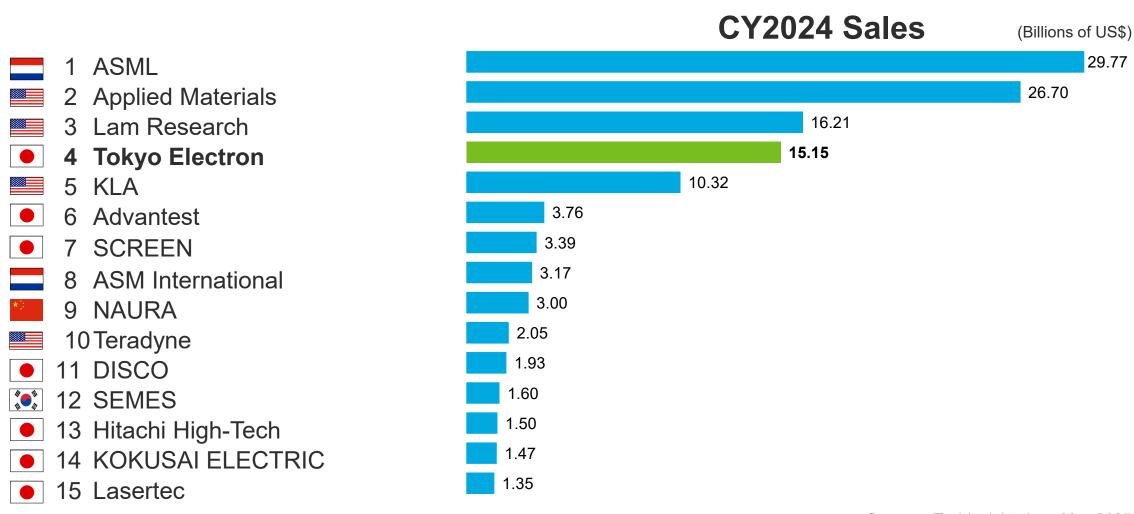

## CY2024 SPE Makers Top 15

Source: TechInsights Inc., May 2025

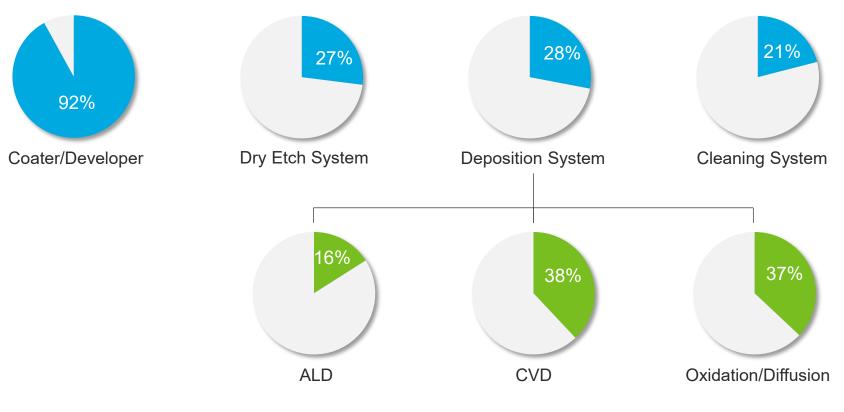

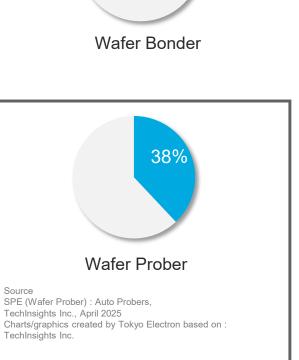

## World Market Share of Major Products (CY2024)

SPE (excluding Wafer Prober): Gartner®, Market Share: Semiconductor Wafer Fab Equipment, Worldwide, 2024, Bob Johnson and Menglin Cao, 21 April 2025, Revenue from Shipments basis. Chart created by TEL based on Gartner research. Gartner research. Calculations performed by TEL.

Coater/Developer: Photoresist Processing (Track), Dry Etch System: Dry Etch, Deposition System: Tube CVD + Atomic Layer Deposition Tools + Oxidation/Diffusion Furnaces + Nontube LPCVD, ALD: Atomic Layer Deposition Tools, CVD: Tube CVD + Nontube LPCVD, Oxidation/Diffusion: Oxidation/diffusion Furnaces, Cleaning System: Single Wafer Processors + Wet Stations + Batch Spray Processors + Scrubbers + Other Clean Equipment, Wafer Bonder: Wafer Bonder,

GARTNER is a registered trademark and service mark of Gartner, Inc. and/or its affiliates in the U.S. and internationally and is used herein with permission. All rights reserved. Gartner does not endorse any vendor, product or service depicted in its research publications, and does not advise technology users to select only those vendors with the highest ratings or other designation. Gartner research publications consist of the opinions of Gartner's research organization and should not be construed as statements of fact. Gartner disclaims all warranties, expressed or implied, with respect to this research, including any warranties of merchantability or fitness for a particular purpose.

The Gartner content described herein (the "Gartner Content") represents research opinion or viewpoints published, as part of a syndicated subscription service, by Gartner, Inc. ("Gartner"), and is not a representation of fact, Gartner Content speaks as of its original publication date (and not as of the date of this Presentation), and the opinions expressed in the Gartner Content are subject to change without notice.

Source

32%

### TEL's Strengths

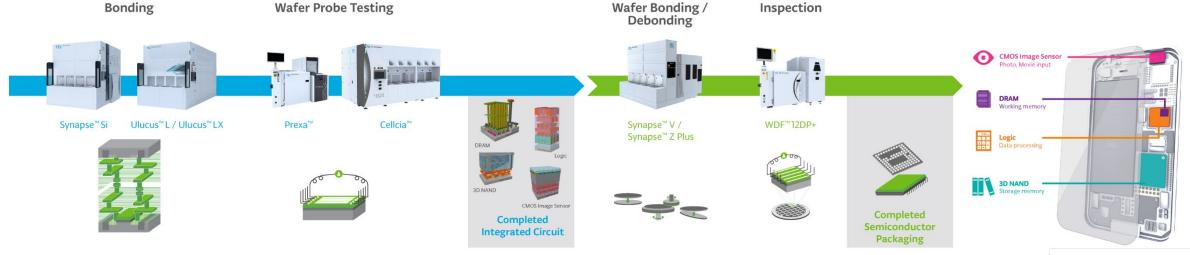

Have products in 4 sequential processes

No.1/No.2

Products with the world's No. 1 or No.2 market share **Major Products & Market Position\***

#1

Developer

Furnace Deposition Deposition

Prober

\*TEL estimate

100%

Market share of coater/developer for EUVL

No.1

Worldwide installed base

Annual increase by about 4,000~6,000 units\*1 Industry's largest installed base 97,000 units\*2

> \*1 As of March 2025 \*2 As of June 2025

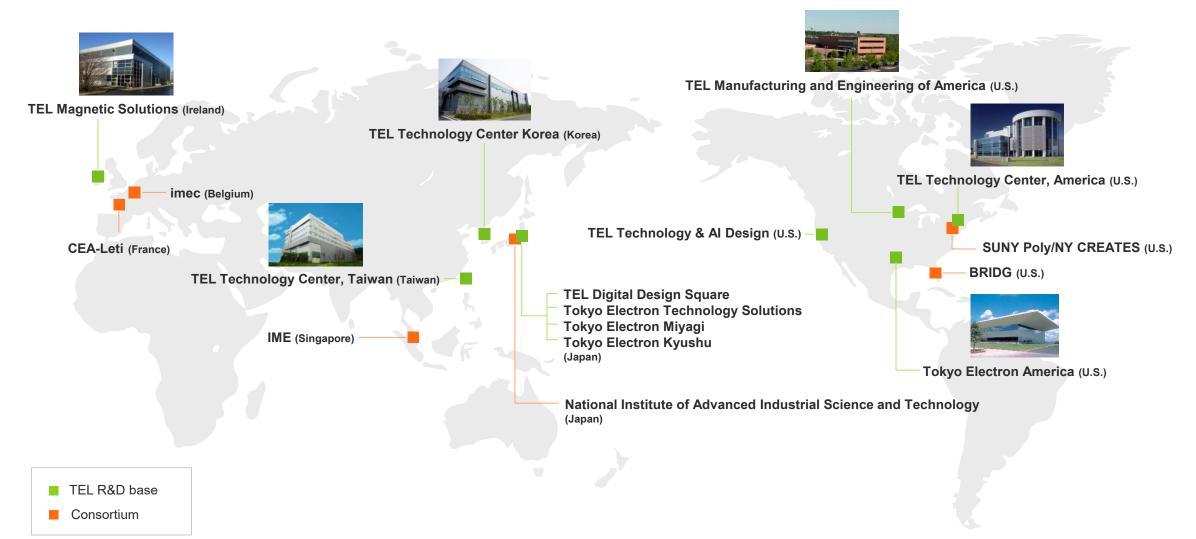

**R&D Map** (As of Apr. 1, 2025)

### Strengthen R&D Capabilities

### Yamanashi R&D building

Deposition system, gas chemical etch system, corporate R&D (Established in July 2023)

### Miyagi R&D building

Etch system (Completion scheduled for spring 2025)

### **Kumamoto R&D building**

Coater/Developers, surface preparation system, Bonder (Completion scheduled for autumn 2025)

### Miyagi Technology Innovation Center

Etch system (Established in September 2021)

### **TEL Digital Design Square**

DX, Software (Began operation in Novenmber 2020)

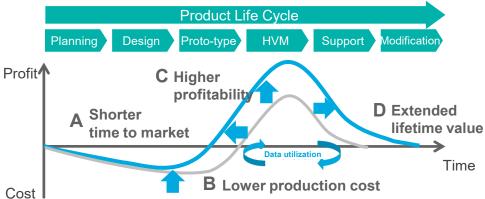

## Continually Pursuing the Best Products and Best Service

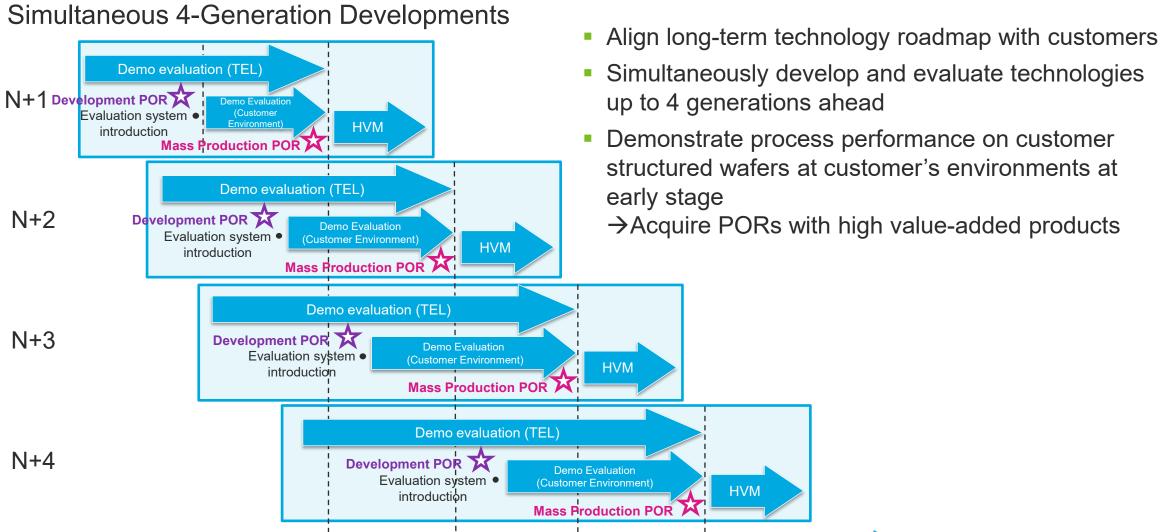

- Share roadmap for next several generations with customers

- Promote early engagement

- Realize maximum yield of customer devices and equipment availability from early stage of customers' mass production and reduce burden on the environment

- Further increase investment in human resources/R&D by raising operational efficiency and driving higher per-employee productivity

- Business development leveraging industry's largest installed base of 97,000 units\*

- TELeMetrics<sup>™</sup> remote maintenance

- Predictive maintenance with machine learning

\* As June 2025

## Maximize Utilization of TEL's Comprehensive Strengths

# Sales

**Customer trust**

# Marketing

Advanced data collection and analysis abilities

**Broad product coverage**

# FS

- Largest installed base in industry: over 97,000 units\*

- Advanced FS

\* As of June 2025

## R&D

- Strong next generation product development

- Process integration

## Manufacturing

- High quality

- Robust supply chain

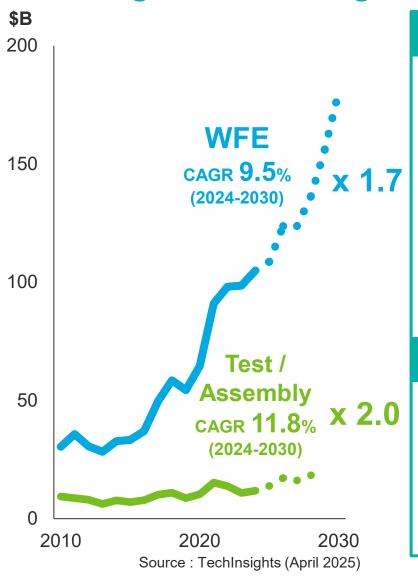

2. Semiconductor and SPE Market Outlook

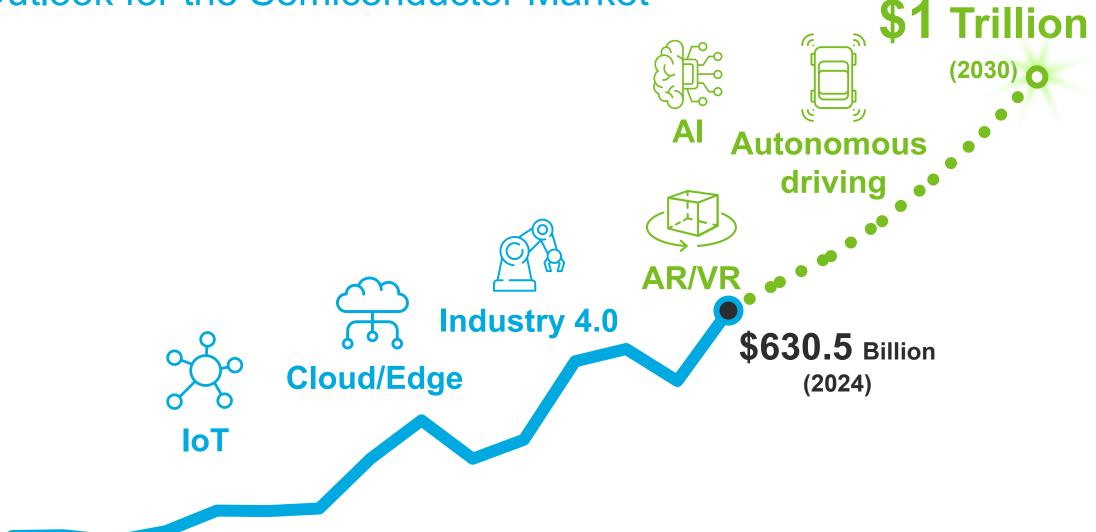

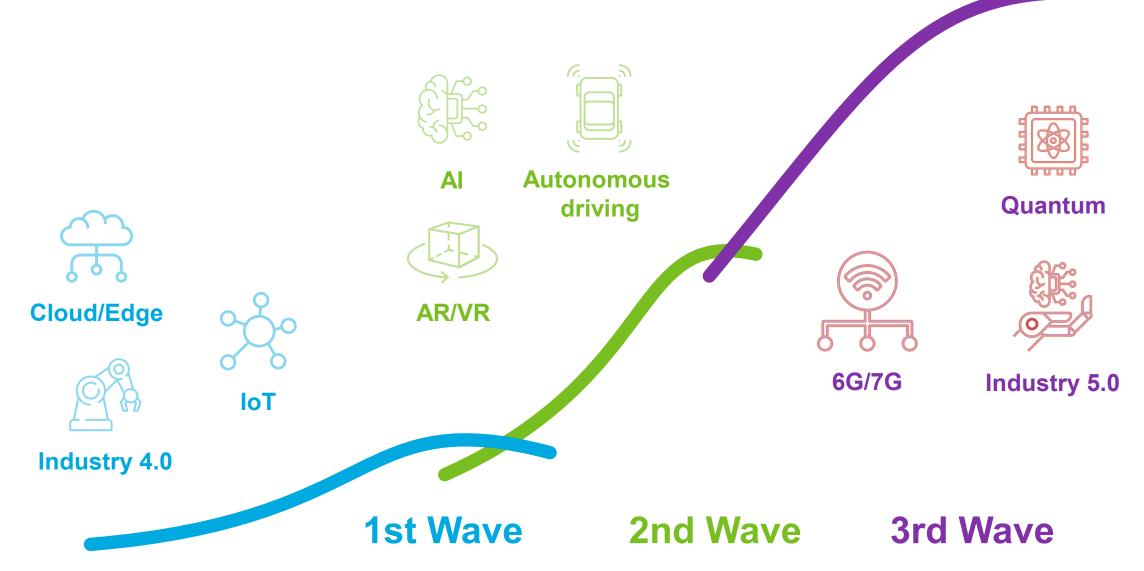

# Outlook for the Semiconductor Market

1st Wave

2nd Wave

### Outlook for the Semiconductor Market

TEL

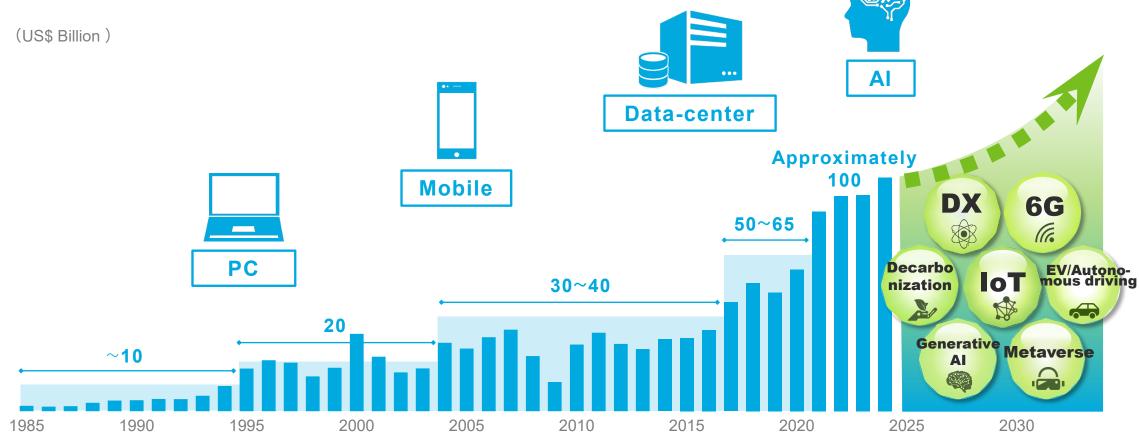

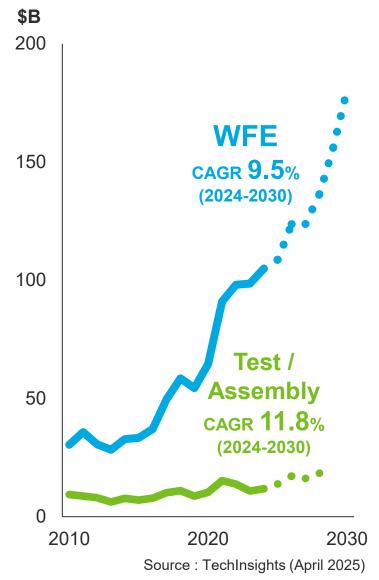

### WFE\* Market

<sup>\*</sup> WFE (Wafer Fab Equipment): The semiconductor production process is divided into front-end production, in which circuits are formed on wafers and inspected, and back-end production, in which wafers are cut into chips, assembled and inspected again. WFE refers to the production equipment used in front-end production and in wafer-level packaging production.

Source: TechInsights Inc. (1985~2024)

WFE Market will grow further with progress of digitalization and evolution of semiconductors

TEL

## Market and Performance Growth (FY2015 to FY2025)

Source: TechInsights Inc.

## Green Future Through Semiconductor Evolution

# Digital & Green-

Higher Speed

Larger Capacity Superior Reliability

Lower Power Consumption

**Physical Scaling**

Heterogeneous Integration

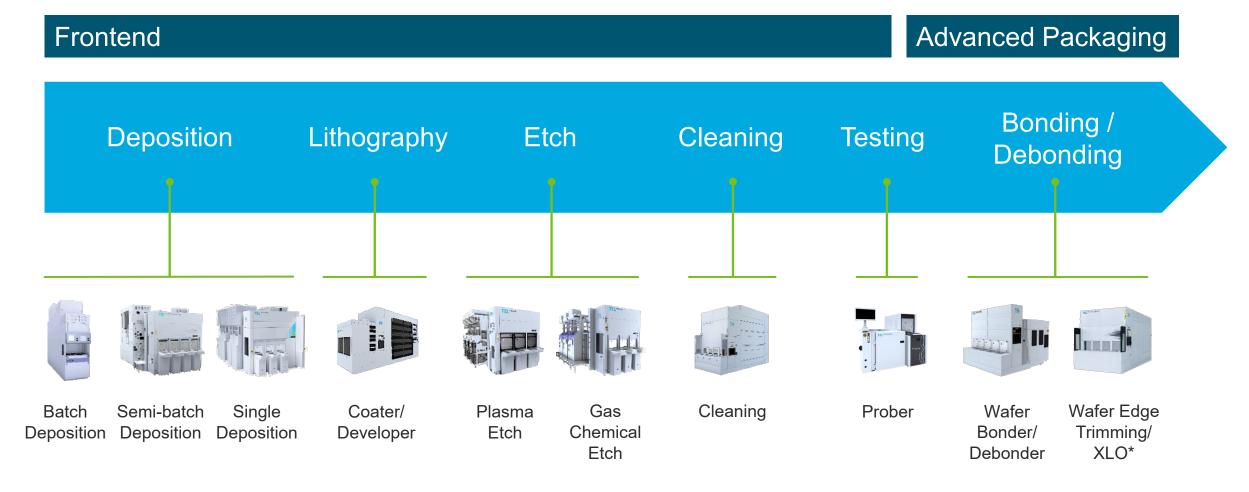

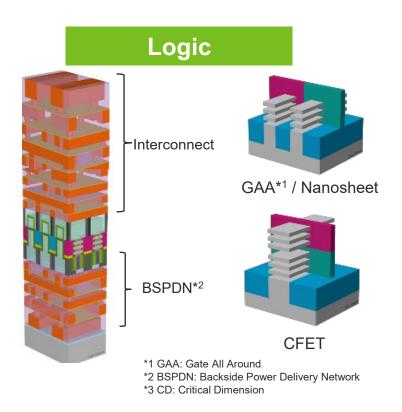

## Physical Scaling x Heterogeneous Integration

Frontend

Logic

GAA \* / CFET

Logic

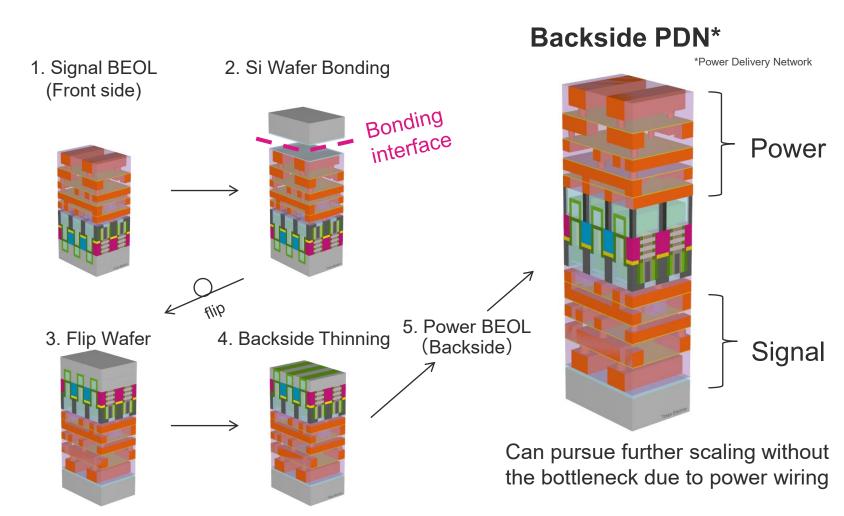

Backside PDN \*

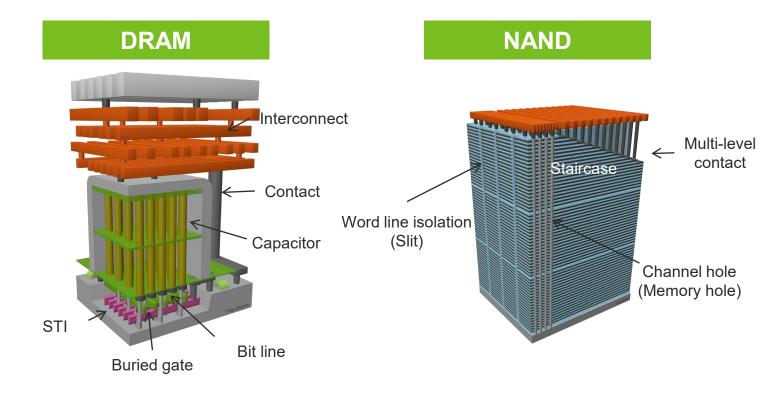

**DRAM**4F<sup>2</sup> VCT \* / 3D DRAM

Super Flat Wafer

Al Semiconductor

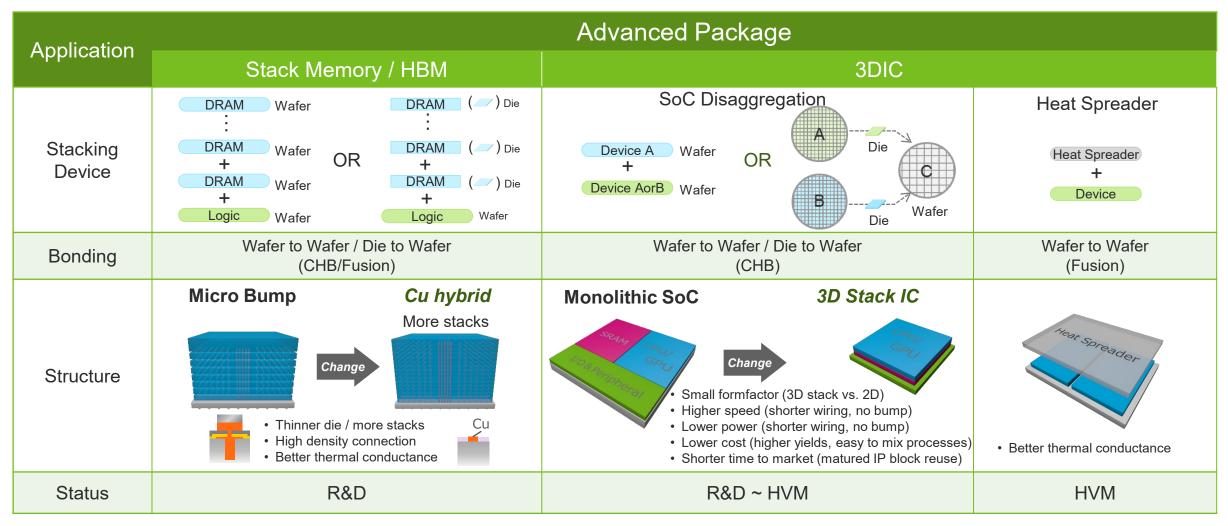

Advanced Packaging

**Heat Spreader**

3DIC Chiplet Integration

Stack Memory HBM, etc.

**Known Good Die**

\* GAA : Gate All Around

<sup>\*</sup> Backside PDN: Backside Power Delivery Network

<sup>\*</sup> VCT : Vertical Channel Transistor

## Expanding Opportunities: Wide Product Portfolio

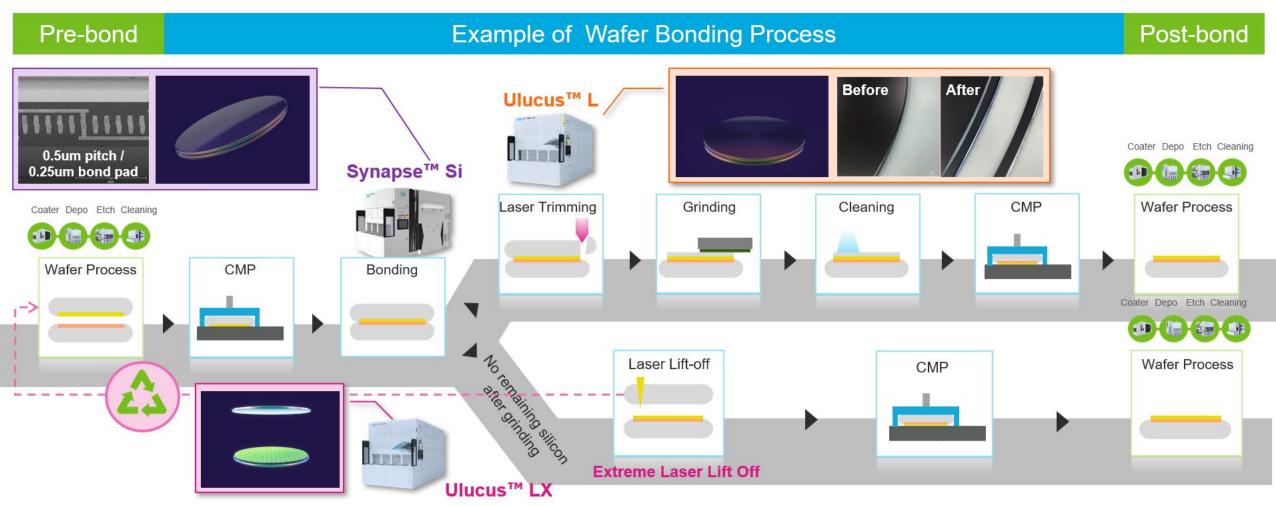

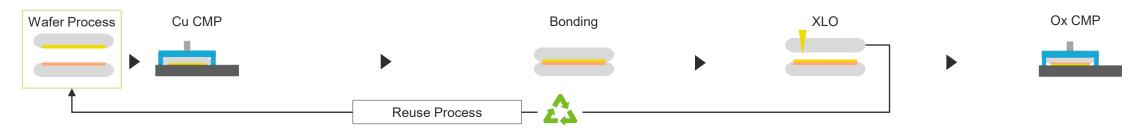

\*XLO: Extreme Laser Lift Off

### Strategic Technologies for Future Growth

### **Frontend**

#### Logic: GAA, BSPDN

- EUV Coater/Developer

- Gas Chemical Etch

- Conductor Etch

- PVD Metal Overburden

- CFET/Inner Spacer

Plasma CVD for filling film

- Double-sided scrubber

- Backside/bevel cleaning

- Pattern Shaping

- Wafer Bonder

- Laser Tool

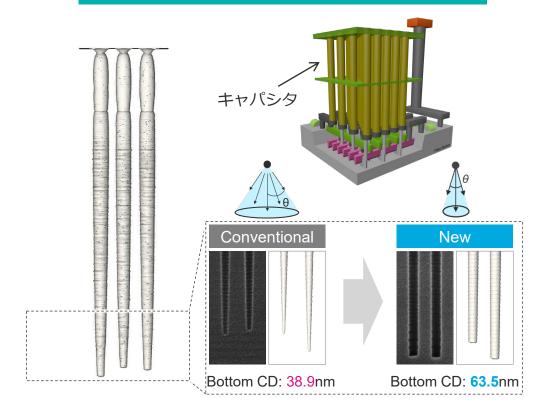

#### DRAM: 2D & 3D DRAM

- EUV Coater/Developer

- Capacitor Mold Etch

- Batch High-k Capacitor deposition

- PVD Metal Hardmask

- Supercritical Cleaning

- Backside/bevel Cleaning

- Wafer Bonder

- Laser Tool

### NAND: Beyond 4xx

- Slit Etch

- Channel Hole Etch (Plug)

- Batch Mo deposition

- Batch Cleaning WL Separation

- Wafer Bonder

- Laser Tool

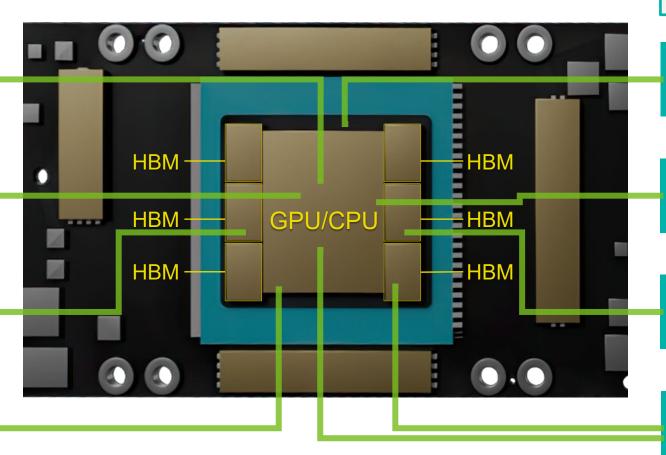

### **Advanced Packaging**

### **Logic Packaging**

- Interposer, Polyimide & PR Coater/Developer

- TDV Etch

- Batch High-k Capacitor depo

- Wafer Bonder

- Laser Tool

#### **HBM Packaging**

- Polyimide & PR Coater/Developer

- Metal Etch for HBM

- Aerosol Cleaning

- Temporary Bonder/Debonder

## Advanced Logic / Memory Test

Prober

3. Corporate Principles and New Medium-term Management Plan

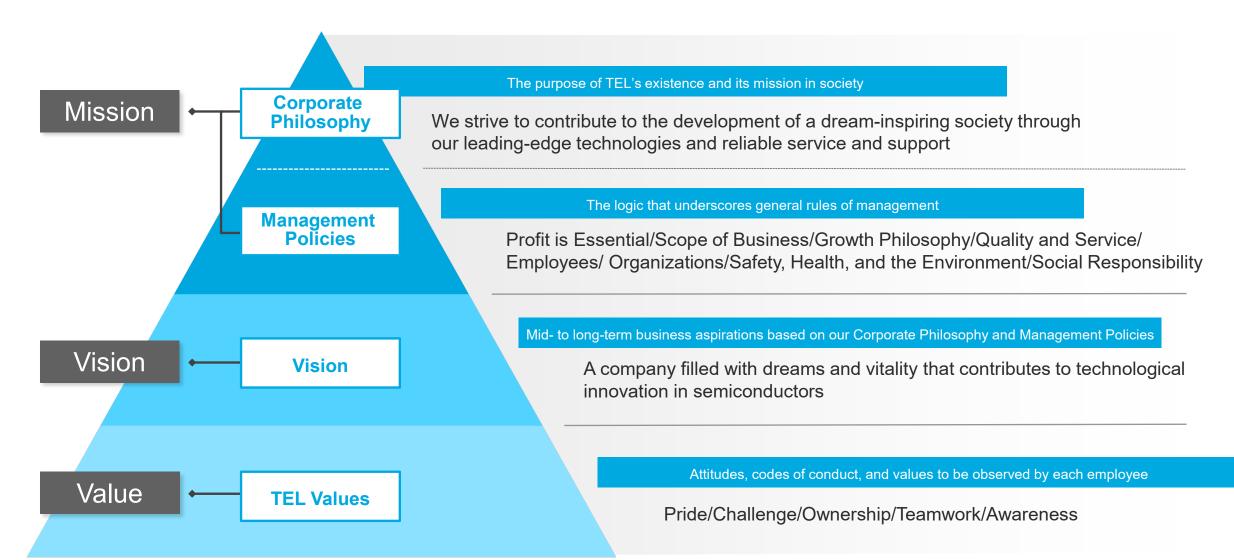

### Corporate Principles System

### Vision

# A company filled with dreams and vitality that contributes to technological innovation in semiconductors

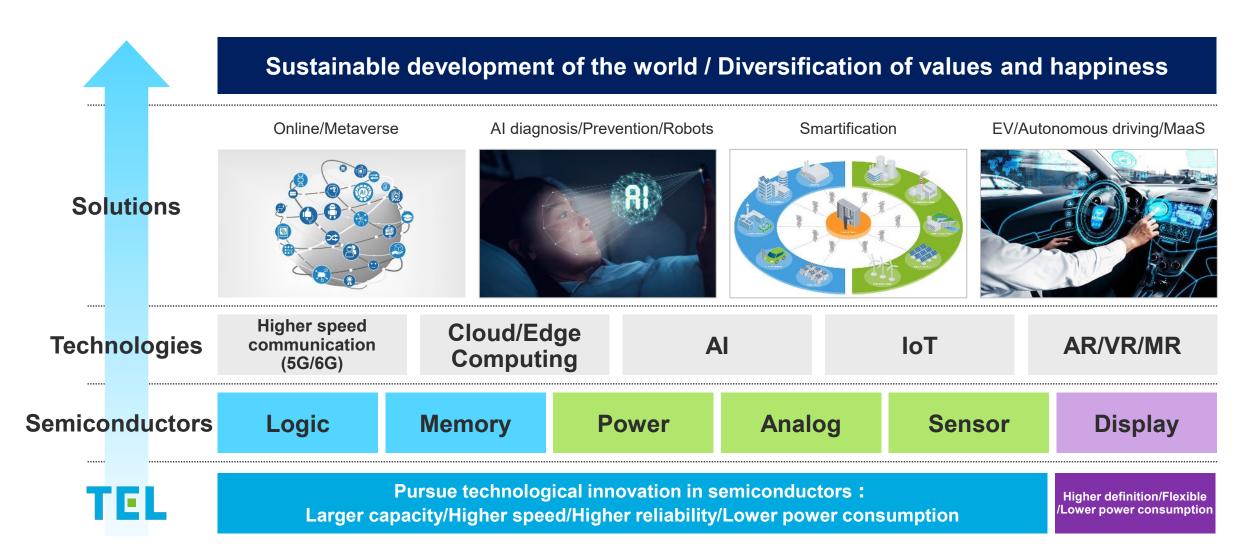

Tokyo Electron pursues technological innovation in semiconductors that supports the sustainable development of the world.

We aim for medium- to long-term profit expansion and continuous corporate value enhancement by utilizing our expertise to continuously create high value-added leading-edge equipment and technical services.

Our corporate growth is enabled by people, and our employees both create and fulfill company values. We work to realize this vision through engagement with our stakeholders.

# Technology Enabling Life

"Technology Enabling Life" is our corporate message that expresses the Corporate Principles which consist of our Corporate Philosophy, Management Policies, Vision and TEL Values.

### **CSV**

(Creating Shared Value)

The concept is to create social and economic value by leveraging corporate expertise to solve social issues, hereby enhancing corporate value and achieving sustainable growth.

- Pursue technological innovation in semiconductors that supports the sustainable development of the world

- Continuously create high value-added leading-edge equipment and technical services

- Medium- to long-term profit expansion and continuous corporate value enhancement

- Engagement with our stakeholders

Realization of Vision = Creating Shared Value in TEL

TEL

### Our Approaches to Social Issues

## Vision & Medium-term Management Plan

**FY2023** FY2027 FY2031 (CY2030) Goals for 2030 Supporting sustainable development in the world 1 Driving the semiconductor market through technological innovation **2** Contributing to a sustainable global environment Realization of Vision Medium- to long-term profit expansion and continuous corporate value enhancement A company filled with dreams and vitality **Engaging with our stakeholders** that contributes to technological innovation in semiconductors Medium-term Management Plan (FY2023-2027) Achievement of Financial Model (Five-year goal toward 2030)

Aiming to achieve the Medium-term Management Plan by FY2027 with a view to realizing Vision in 2030

TEL

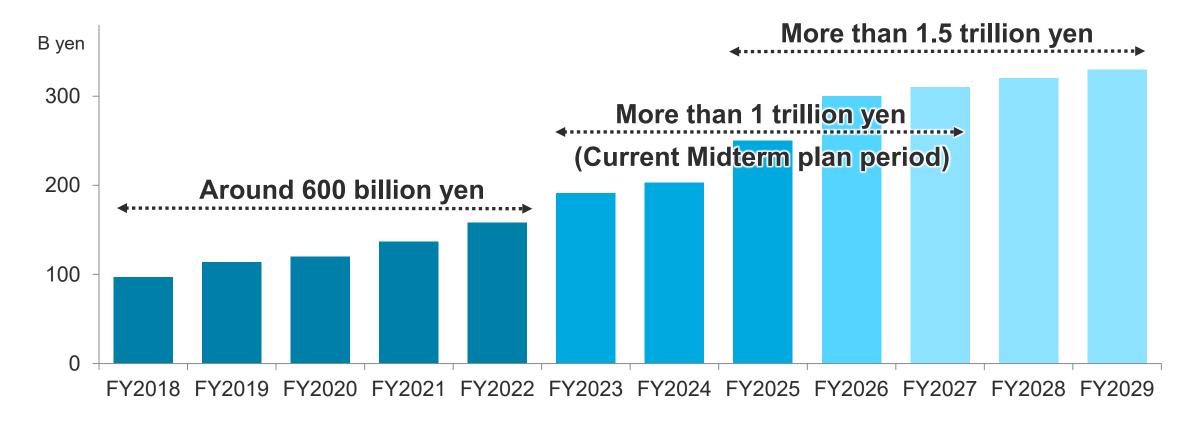

## The New Medium-term Management Plan: Financial Targets

| Financial Targets (FY2023 - FY2027) |                  |  |

|-------------------------------------|------------------|--|

| Net sales                           | ≥ 3 trillion yen |  |

| OP margin                           | ≥ 35%            |  |

| ROE                                 | ≥ 30%            |  |

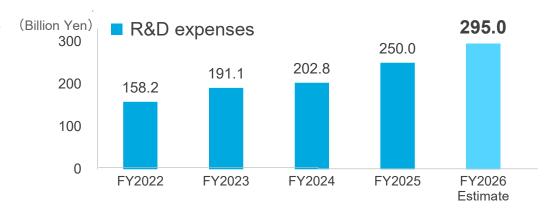

### Aggressive Investment in R&D

Driving the creation of high-value next-generation products through further growth investments

TEL

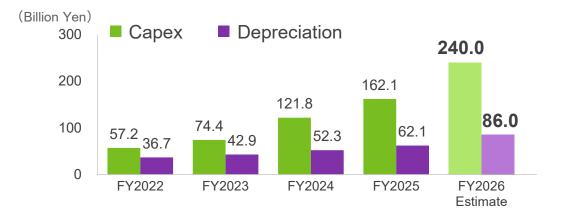

# Investment for Growth Visioning beyond the Midterm Plan (FY2025 to FY2029)

**R&D Investment**

Capex

Recruitment

1.5 trillion yen

700 billion yen

10,000 people year

4. Business Environment and Financial Estimates

### Market Environment and Business Progress

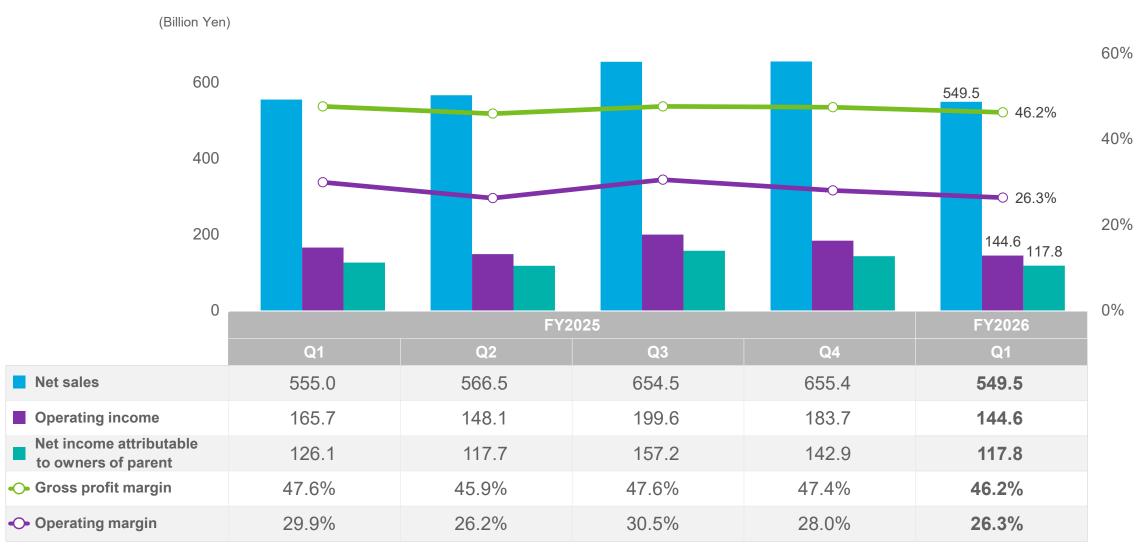

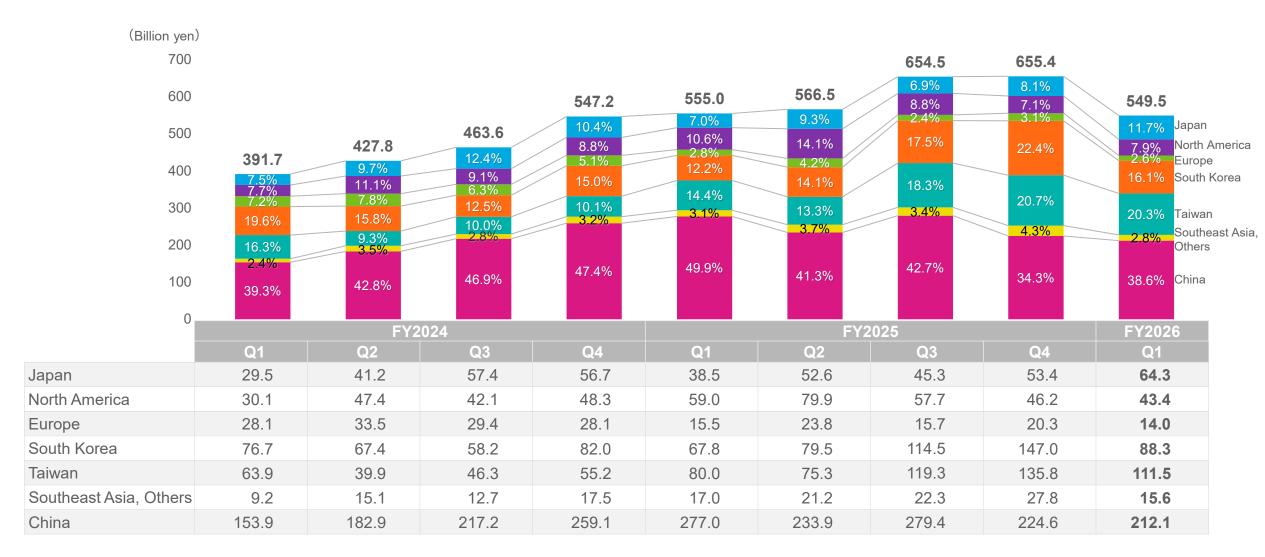

- Q1 FY2026: Business progressed as planned

- Both net sales and profit proceeded as planned

- Net sales 549.5 B yen, Operating profit 144.6 B yen, Operating profit margin 26.3%

- POR\* acquisition and development of strategic products for future growth on track

- New low-resistance metal deposition tool: evaluation in progress with multiple NAND customers

- 3D integration tools including extreme laser lift off: negotiation underway

- Construction of new development building in Tokyo Electron Miyagi completed

- H1 FY2026 business outlook: no change

- Net sales 1.15 T yen, Operating profit 288.0 B yen, Operating profit margin 25.0%

- CY2025 WFE: In line with expectations

- Reflecting currency fluctuations, etc., WFE forecast has been revised from \$110B in April, to \$115B

## Market Environment and Business Progress

Trends in H1 CY2026 (January – June) :

WFE growth rate of -5% for FY2026 due to productivity improvements resulting from improved customer yields, optimization of the supply-demand balance with an eye on profits, and a shift from upfront investments to more steady investments

- Some leading-edge logic customers are revising their capex plan

- Emerging Chinese chip manufacturers are scaling back their legacy investments

- NAND investment plans are changing based on careful considerations of supply/demand balance

- Although demand for HBM\* is strong, investment plans are also being revised due to production technology and customer yield improvements

- Delay in full transition investment from DRAM DDR4 to DDR5

TEL

<sup>\*</sup> HBM (High Bandwidth Memory)

# FY2026 Financial Estimates

(Billion Yen)

|                                             | FY2025                  |                        | Reference: FY2026 (Forecast announced on 4/30) |                         |                           |                            |                         |                         |

|---------------------------------------------|-------------------------|------------------------|------------------------------------------------|-------------------------|---------------------------|----------------------------|-------------------------|-------------------------|

|                                             | (Actual)                | H1                     | H2                                             | Full Year               | vs FY2025                 | Adjustments*               | H2                      | Full Year               |

| Net sales                                   | 2,431.5                 | 1,150.0                | 1,200.0                                        | 2,350.0                 | -3.4%                     | -250.0                     | 1,450.0                 | 2,600.0                 |

| Gross profit Gross profit margin            | 1,146.2<br>47.1%        | 527.0<br>45.8%         | 539.0<br>44.9%                                 | 1,066.0<br>45.4%        | -7.0%<br>-1.7pts          | -162.0<br>-1.8 pts         | 701.0<br>48.3%          | 1,228.0<br>47.2%        |

| SG&A expenses<br>R&D<br>Other than R&D      | 448.9<br>250.0<br>198.9 | 239.0<br>140.0<br>99.0 | 257.0<br>155.0<br>102.0                        | 496.0<br>295.0<br>201.0 | +10.5%<br>+18.0%<br>+1.0% | <b>-5.0</b><br>-5.0<br>0.0 | 262.0<br>160.0<br>102.0 | 501.0<br>300.0<br>201.0 |

| Operating income Operating margin           | 697.3<br>28.7%          | 288.0<br>25.0%         | 282.0<br>23.5%                                 | 570.0<br>24.3%          | -18.3%<br>-4.4pts         | -157.0<br>-3.7pts          | 439.0<br>30.3%          | 727.0<br>28.0%          |

| Income before income taxes                  | 706.1                   | 293.0                  | 286.0                                          | 579.0                   | -18.0%                    | -157.0                     | 443.0                   | 736.0                   |

| Net income attributable to owners of parent | 544.1                   | 224.0                  | 220.0                                          | 444.0                   | -18.4%                    | -122.0                     | 342.0                   | 566.0                   |

| Net income per share (Yen)                  | 1,182.40                | 488.93                 | -                                              | 969.12                  | -213.28                   | -266.39                    | -                       | 1,235.51                |

<sup>\*</sup> Changes from the figures announced on April 30, 2025

#### Revised forecast to reflect customer investment status

TEL

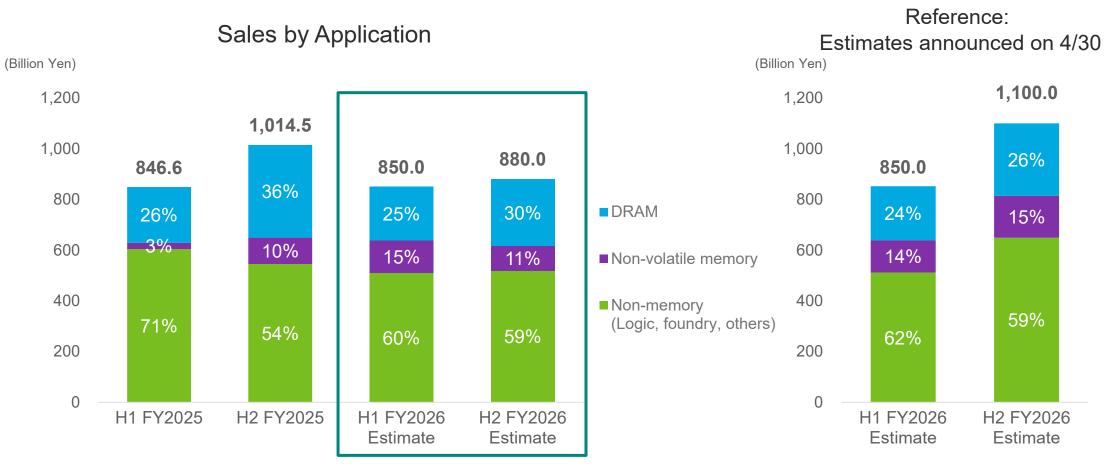

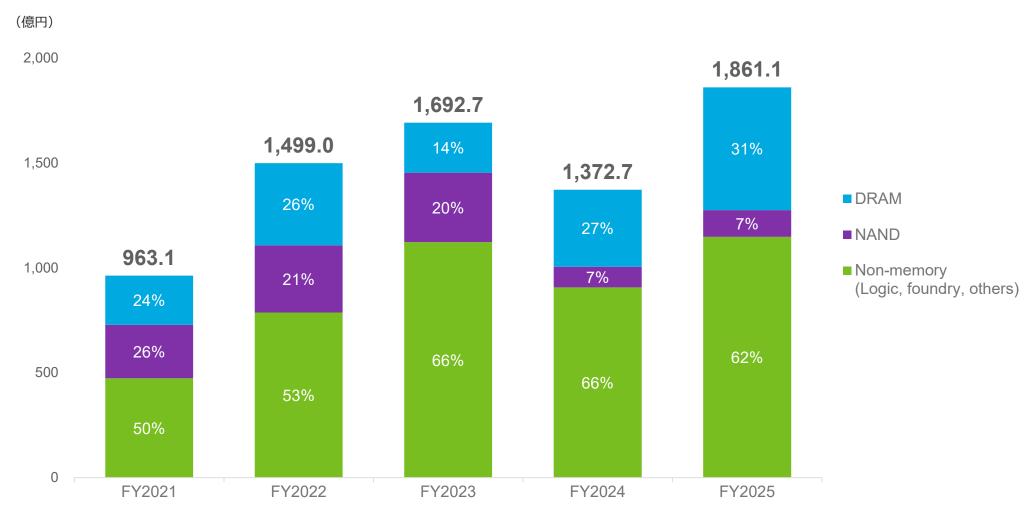

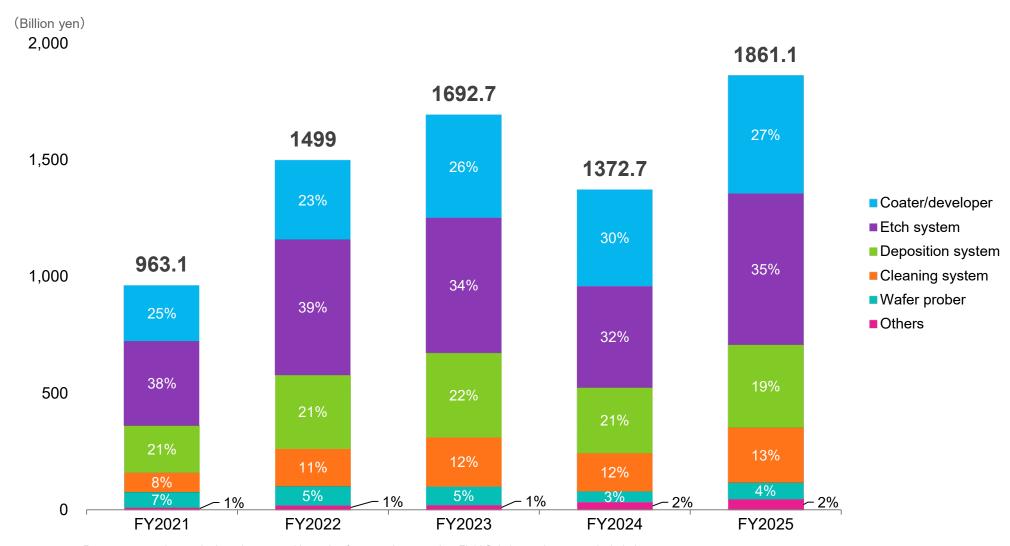

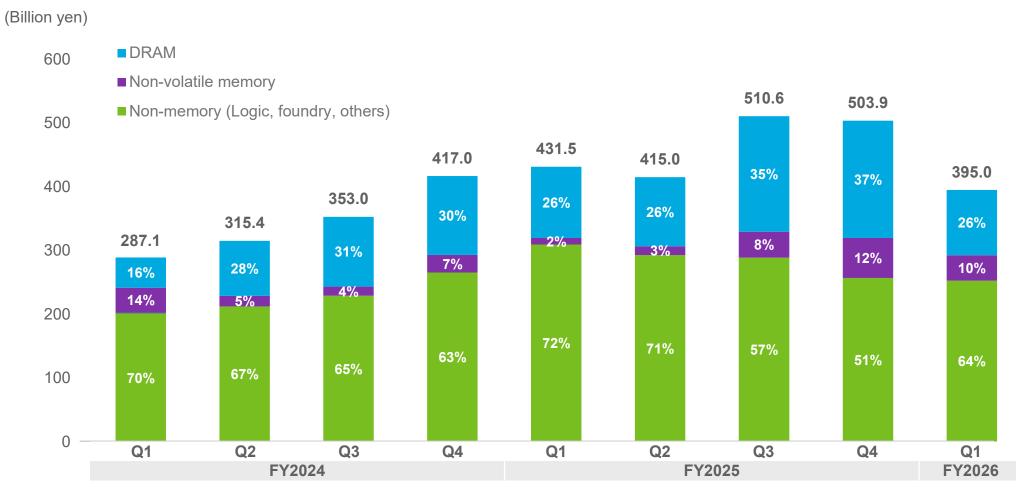

# FY2026 SPE New Equipment Sales Forecast

Percentages on the graph show the composition ratio of new equipment sales. Field solutions sales are not included.

Revised H2 FY2026 forecast reflecting the latest investment trend

TEL

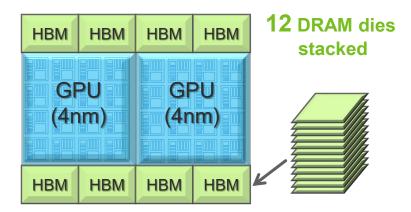

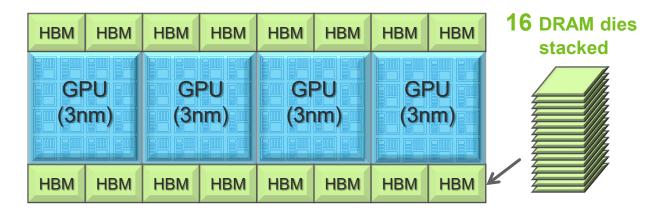

# Cutting-edge Chips Indispensable for Al Servers Growth Drivers for CY2026 (FY2027)

**CY2025**

CY2027

200 billion transistors

Memory capacity 288GB

GPU: Graphic Processing Unit HBM: High Bandwidth Memory

500 billion transistors

Memory capacity 1TB (1,024GB)

TEL estimates

Technology innovation proceeds, increasing the # of transistors by 2.5x, memory capacity by 4x, shifting from two 4nm-GPUs to four 3nm-GPUs, and 12- to 16-stack HBMs in 2 years to come

# FY2026 R&D Expenses and Capex Plan

#### **New Development Building**

Etch system

Kurokawa-gun, Miyagi Prefecture Completed in April 2025

#### **Tohoku Production and Logistics Center**

Deposition system

Oshu-city, Iwate Prefecture

Completion scheduled for autumn 2025

#### **New Development Building**

Coater/developer, cleaning system, bonder

Koshi-city, Kumamoto Prefecture Completion scheduled for autumn 2025

#### **New Production Building**

Etch system

Kurokawa-gun, Miyagi Prefecture Completion scheduled for summer 2027

Semiconductors for AI servers drive technology innovation, fueling expanding demand. R&D and capital investments to proceed as scheduled

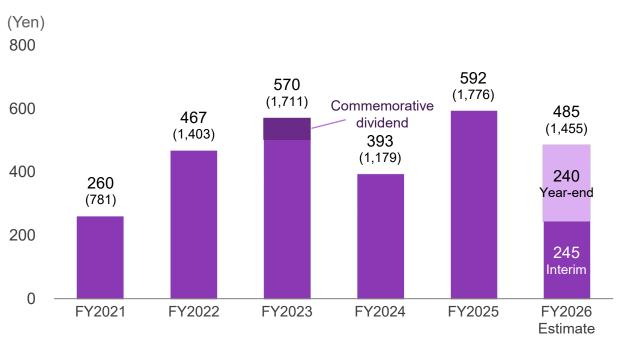

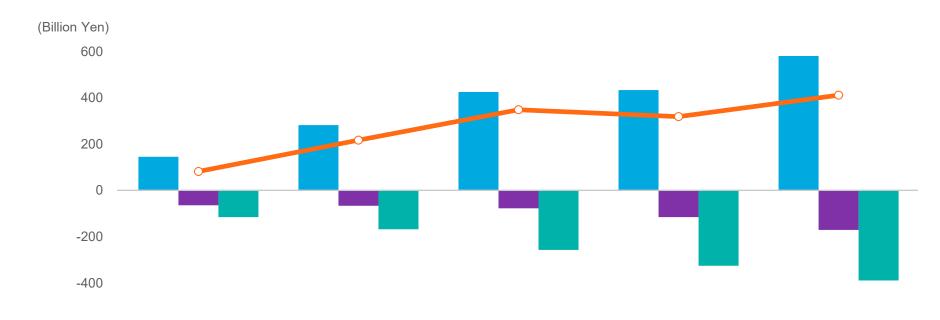

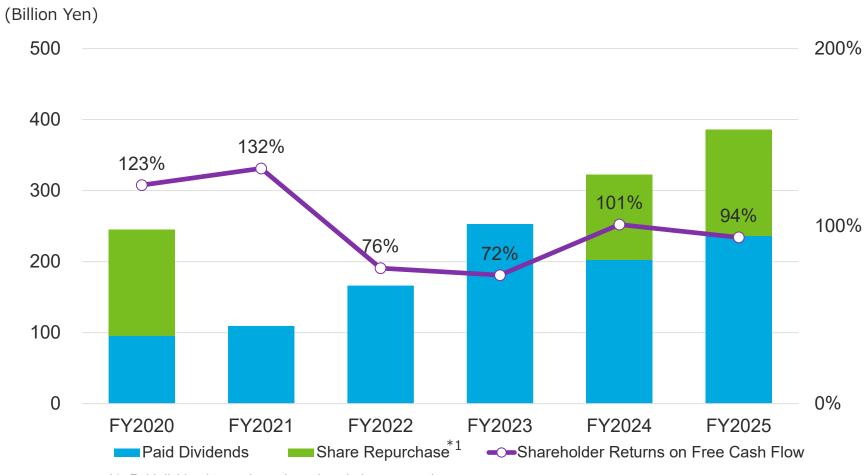

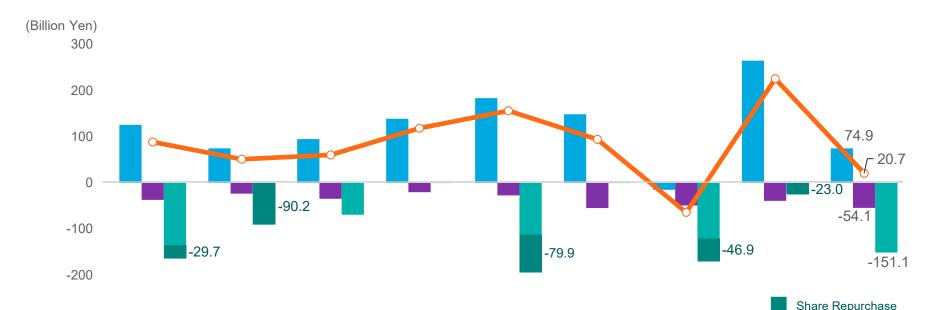

## FY2026 Dividend Forecast

#### Dividend per Share

#### **TEL** shareholder return policy

#### Dividend payout ratio: 50%

Annual DPS of not less than 50 yen\*

We will review our dividend policy if the company does not generate net income for two consecutive fiscal years

We will flexibly consider share buybacks

\*Due to the stock split on April 1, 2023, the amount has been changed from 150 yen to 50 yen.

- Dividends per share from FY2020 to FY2023 are calculated on the assumption that the stock split was conducted at the beginning of FY2020.

- FY2023 includes the 60<sup>th</sup> anniversary commemorative dividends.

- Amounts before the stock split are shown in parentheses.

Full-year dividends are expected to be 485 yen per share

# 5. Sustainability

# **Sustainability Initiatives**

The 14 material issues (key issues) that require prioritized attention and actions are identified to implement sustainability initiatives through our business operation and contribute to the resolution of industrial and social issues.

Respect for Human Rights

Climate Change and Net Zero

Product Energy Efficiency

Best Products with Innovative Technology

Best Technical Service with High Added Value

**Customer Satisfaction and Trust**

Supplier Relationship

**Employee Engagement**

Safety First Operation

**Quality Management**

Compliance

**Ethical Behavior**

Information Security

Enterprise Risk Management

# Risk Management

Sustainability-focused management aiming to remain a company that is loved and trusted by all stakeholders. Promotion of technological innovation of semiconductors and reduction of environmental impact in supply chain

TEL

# **Environmental Approaches**

# Net Zero

**Target**

Scope 1, 2 & 3 by 2040

Scope 1&2: CO2 Emissions from energy use such as electricity in business activities

Scope 3 : CO2 Emissions from the use and disposal of sold equipment, material purchases and logistics, etc.

# E-COMPASS \*\*

Environmental Co-Creation by Material, Process and Subcomponent Solutions

#### **Semiconductors**

Pursuing higher device performance and lower power consumption

#### **Products**

Achieving both high process performance and environmental performance of the equipment

#### **Business activities**

Reduction of CO<sub>2</sub> emissions in all business activities

Promoting technological innovation of semiconductors and reducing environmental impact throughout the supply chain

# Safety & Quality

#### **Safety**

Under the "Safety First" slogan, everyone at Tokyo Electron, from top management to field representative, is actively and continuously improving safety and promoting health, giving safety and health the highest priority when carrying out different types of operations such as development, manufacturing, transportation, installation and maintenance.

Safety Goals (by FY2027) **TCIR ≤ 0.1**  TCIR: Total Case Incident Rate (Number of workplace injuries per 200,000 work hours)

#### **Incident Prevention Initiatives**

- Experiential training and VR (Virtual Reality)

- Comprehensive safety inspections

- Feedback on safety specifications

- Safety activities for suppliers

#### Quality

The Tokyo Electron Group seeks to provide the highest-quality products and services. This pursuit of quality begins at development and continues through all manufacturing, installation, maintenance, sales and support processes. Our employees must work to deliver quality products, quality services and innovative solutions that enable customer success.

# TEL Values as codes of conduct

# **Engagement**

#### Career

# Corporate growth is enabled by People, and our employees both create and fulfill company values

#### Retention

#### Work-life balance

# Diversity, Equity and Inclusion

Global · Generation · Gender

# **Human Rights Initiatives**

The five focus areas in human rights (Tokyo Electron Group Human Rights Policy)

Freedom, equality & non-discrimination

Freely chosen employment

Product safety & workplace health and safety

Freedom of association Appropriate working hours & breaks/ holidays/vacations

Human Rights Due Diligence

Remediation

Commitment

**Commitment to respecting**

human rights

Assessment of human rights risks in business and supply chains

**Assessment**

Actions to reduce risks based on assessment results

Regular disclosure of

Report

- Revision of Tokyo Electron **Group Human Rights Policy**

- Human rights risk assessment

- Program development and review

- - according to issues

information

- Feedback sheet publication Publication of the Integrated Report Human rights impact assessment

- Postings on the website

- Awareness and implementation

- Education

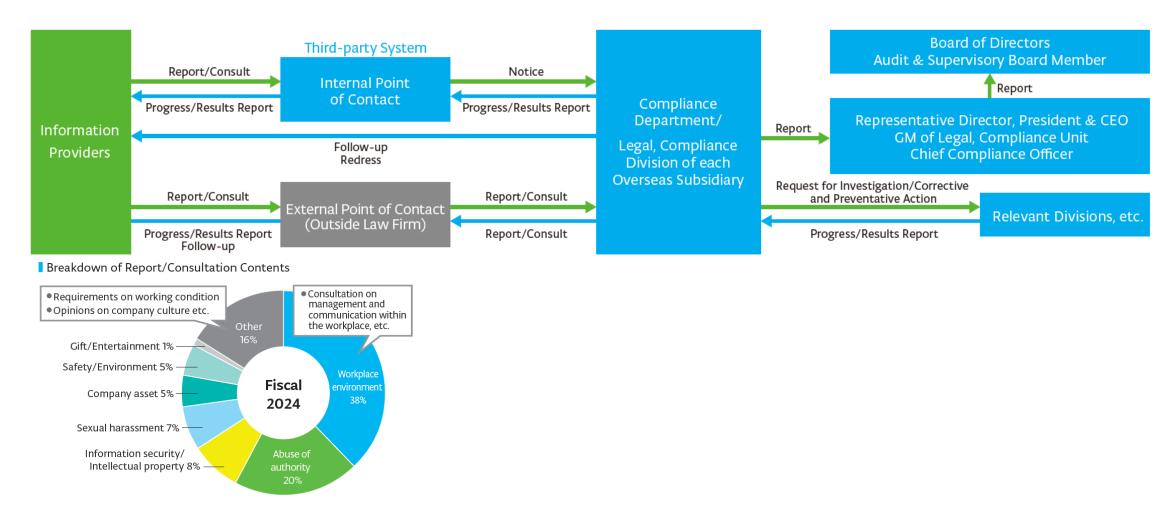

# **Internal Reporting System**

Respect for human rights with a strong sense of integrity

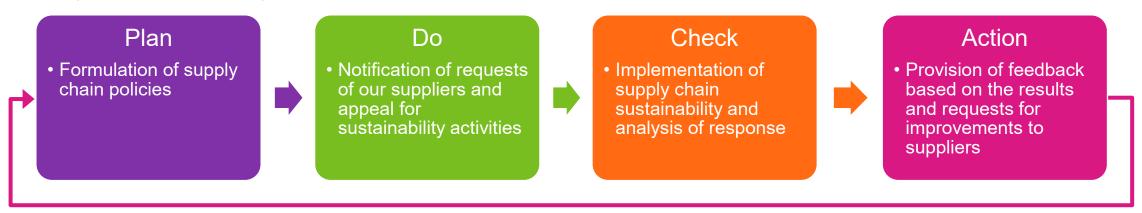

# **Supply Chain Management**

Supply chain sustainability process

- Annual Sustainability Assessment

- Assessment base on RBA code of conduct

- Corrective Action Plans

- RBA Audit

- At primary manufacturing sites

- Continuous improvement in respective operations

Pursuit of sustainability conscious operations throughout the supply chain

TEL

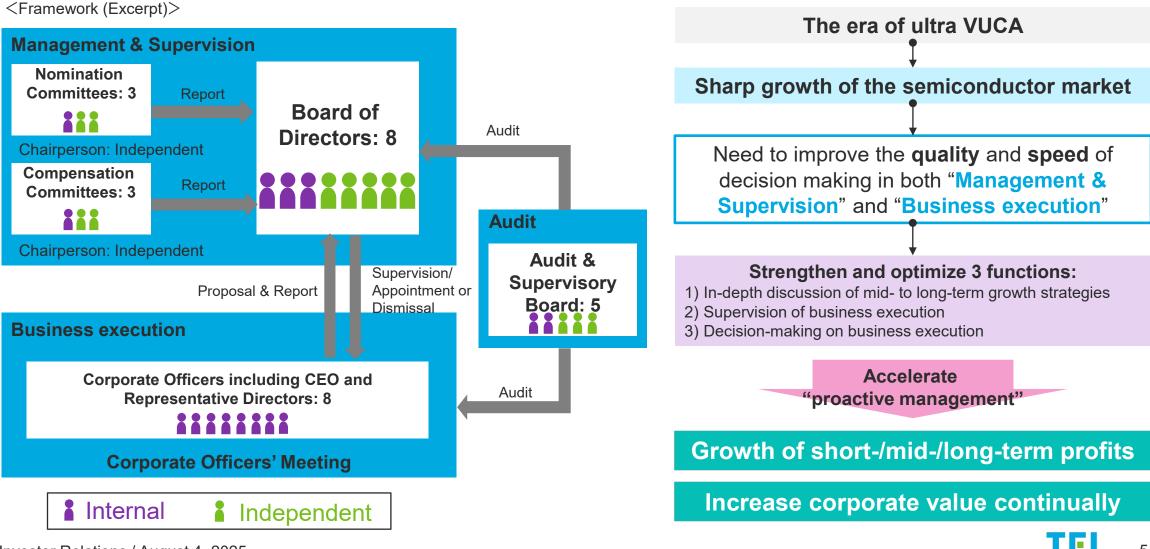

# Corporate Governance Framework (Audit & Supervisory Board System)

## Evaluation of the Effectiveness of the Board of Directors

Survey administered to all corporate directors and Audit & Supervisory Board members

Interviews of all corporate directors and Audit & Supervisory Board members by external experts

Report by external experts

Deliberations at internal meetings

Meetings for exchanges of opinions by independent directors and independent Audit & Supervisory Board members

Discussion and self-evaluation by the Board of Directors

Internal and external experts analyze and evaluate the effectiveness of the Board of Directors

## **Global Initiatives**

#### **Sustainable Development Goals (SDGs)**

Clarify initiatives through business by materiality and deploy company-wide

日 働きがいも 経済成長も

Tokyo Electron supports the SDGs

#### **Participation in International Initiatives**

Signed the UN Global Compact, joined the Responsible Business Alliance (RBA), endorsed the Task Force on Climate-related Financial Disclosures (TCFD)

**WE SUPPORT**

#### **External Evaluation on our ESG Initiatives**

Highly rated by evaluation organizations around the world

Member of **Dow Jones** Sustainability Indices

Powered by the S&P Global CSA

MSCI ESG Leaders

The inclusion of Tokyo Electron Limited in any MSCI Index, and the use of MSC logos, trademarks, service marks or Index names herein, do not constitute a sponsorship, endorsement or promotion of Tokyo Electron Limited by MSCI or any of its affiliates. The MSCI Indexes are the exclusive property of MSCI. MSCI and

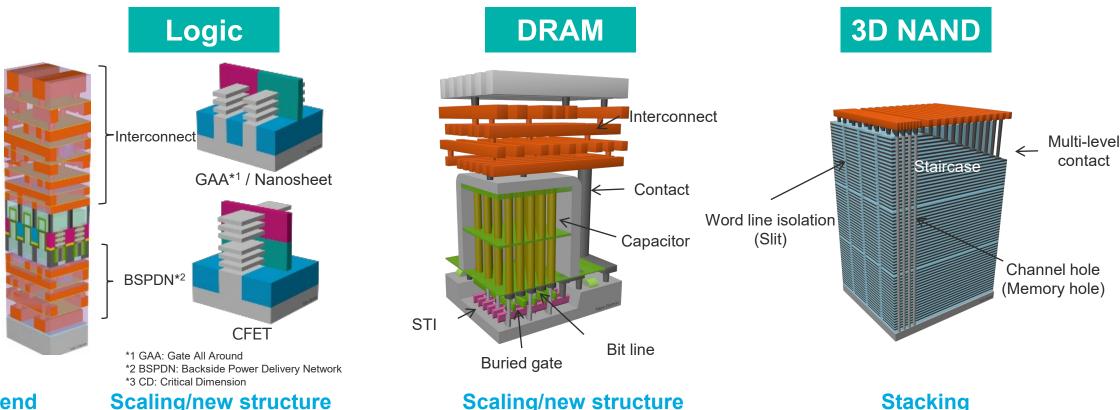

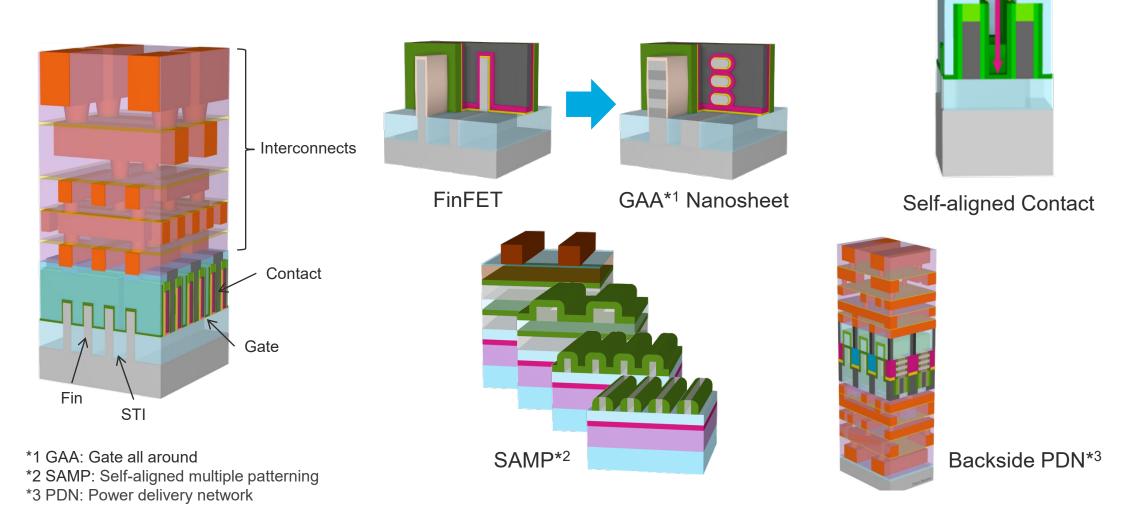

6. Diversifying Semiconductor Technology

~ Technology Roadmap~

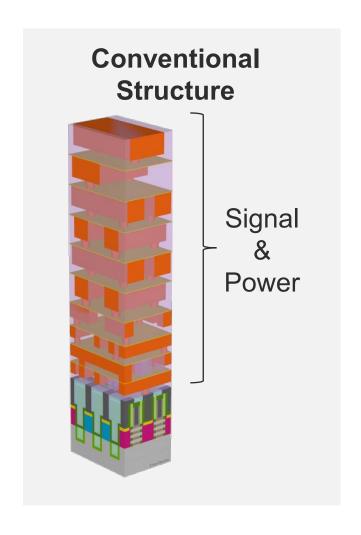

# Semiconductor Devices: Direction of Development

# Through miniaturization with structural changes

- Lowered cost per transistor

- Lower power consumption

- Higher speed

#### Through miniaturization

- Lower cost per bit

- Lower power consumption

- · Higher speed

#### Through new structures

Lower cost per bit

#### Through high stacking

Lower cost per bit

# Logic Technology Roadmap (Generic)

[1] Chih-Hao Chang (TSMC) et al., IEDM 2022

[2] Shien-Yang Wu (TSMC) et al., IEDM 2022 [3] Sandy Liao (TSMC) et al., IEDM 2024

[4] Mertens and Horiguchi (imec), EDTM 2024

Source: TEL estimates

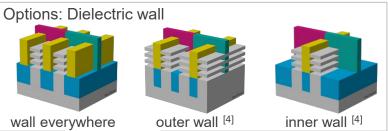

|                              | <u> </u>                                  |             |                             | wall everywnere             | outer wall [4]                             | inner waii [4]            |                           | source: TEL estimates                                                                        |

|------------------------------|-------------------------------------------|-------------|-----------------------------|-----------------------------|--------------------------------------------|---------------------------|---------------------------|----------------------------------------------------------------------------------------------|

| Year of HVM<br>(20k/month)   | 2022~24                                   | 2025~2026   | 2027~28                     | 2029~30                     | 2031~32                                    | 2033~34                   | 2035~36                   | 2037~38                                                                                      |

| Node                         | 3nm                                       | 2nm/18A/16A | 14A                         | 10A                         | 7A                                         | 5A                        | 3A                        | 2A                                                                                           |

|                              | 2~1 Fin                                   | GAA NS      | GAA NS scalir               | ng GAA NS extension         | CFET                                       | 2 <sup>nd</sup> Gen. CFET | 3 <sup>rd</sup> Gen. CFET | 2D material stack                                                                            |

| Transistor                   |                                           |             |                             |                             |                                            |                           |                           | IL/HK  LL/HK  2D material: TMDC  MoS <sub>2</sub> , WS <sub>2</sub> , MoSe <sub>2</sub> etc. |

| Poly Pitch [nm]              | 48~45 <sup>[1]</sup>                      |             | 4                           | 45~42 48 [3] ~42            |                                            | 45                        | ~39                       | 36                                                                                           |

| Min. Metal Pitch [nm]        | 23 [2]                                    |             | 20                          | 18                          | 17                                         | 16                        | 14                        | 12                                                                                           |

| Interconnect<br>booster      | Cu Barrier/Seed CIP<br>Backside PDN (HPC) |             | Cu CIP or<br>Ru subtractive | Ru subtractive AR>3, Airgap | New alloy<br>AR>5, Airgap, BEOL Transistor |                           | ransistor                 |                                                                                              |

| EUV Patterning<br>Technology | EUV MP*1, SE*2                            |             | EUV MP, S<br>High-NA S      |                             |                                            |                           | E                         |                                                                                              |

| Resist                       |                                           | CAR*3       |                             | CAR (+MOR*4)                |                                            | CAR-                      | +MOR                      |                                                                                              |

\*1 MP: Multi-Patterning, \*2 SE: Single-Exposure, \*3 CAR: Chemically Amplified Resist, \*4 MOR: Metal Oxide Resist

Logic scaling will continue by changing transistor structure and material evolution

# DRAM Technology Roadmap (Generic)

| Divini recimology i todadinap (denenc) |                        |                 |                        |                                        |                                     |                |                                                                  |      | So         | urce: TEL estir | mates |           |

|----------------------------------------|------------------------|-----------------|------------------------|----------------------------------------|-------------------------------------|----------------|------------------------------------------------------------------|------|------------|-----------------|-------|-----------|

| Year of HVM<br>(20k/month)             | 2023-24                | 2025            | 2026                   | 2027                                   | 2027 2028                           |                | 2030                                                             | 2031 | 2032       | 2033            | 2034  | 2035      |

| Node                                   | 1b                     | 1c              | 1d                     | 0                                      | 0a                                  |                | 0c                                                               |      | 0d         | 0               | е     |           |

|                                        |                        | 2D              |                        |                                        |                                     |                |                                                                  |      |            |                 |       |           |

| Cell layout /                          |                        | 6F <sup>2</sup> | 4F <sup>2</sup>        | <sup>2</sup> VCT* [1,2]                |                                     |                |                                                                  |      | 3D         | hil             |       |           |

| Structure                              |                        |                 |                        | ************************************** | Promote                             | [1] Seokhan Pa | nnel Transistor<br>ark (Samsung) et al.,<br>(Samsung) et al., IE |      |            |                 |       |           |

| F [nm] in 6F <sup>2</sup>              | 13~12.5                | 12~11           | 10                     | 9                                      | 9                                   |                | 7 (3D ~1xxL                                                      |      | (3D ~1xxL) | _) (3D >1yyL)   |       |           |

| Cap. pitch [nm]                        | 39~37.5                | 36~33           | 30                     | 2                                      | 27                                  |                | 21                                                               |      |            | 4               |       | Canacitan |

| Cap. A.R.                              | >50                    | >55             | >65                    | >7                                     | 70                                  | >75            | >{                                                               | 30   |            | A.R.            |       | Capacitor |

| Cap. Mat.                              | ZrAl                   | HfO             |                        |                                        | Alternative (HfZrO Anti Ferro. etc) |                |                                                                  |      |            |                 |       |           |

| WL                                     | Ti                     | N               | Poly-Si                |                                        | Low R met                           | al             |                                                                  |      |            | WL              |       |           |

| Peri. CMOS                             |                        | HKMG            | nMOS HKMG<br>pMOS      | Bon                                    | ding                                |                |                                                                  |      |            | FinFET          |       |           |

| НВМ                                    | HBM3E<br>(8/12Hi,24/36 | GB)             | HBM4<br>(12/16Hi,36/48 | GB)                                    | HBM4E<br>(16Hi,64GB)                |                | HBM5<br>(16,20Hi, 64/80                                          | GB)  | HBM5E      |                 | HBM6  |           |

# NAND Technology Roadmap (Generic)

|                            | TWITE Tooming by Hoadmap (Coment) |                   |         |      |                                |                         |        |                 |                      | S    | ource: TEL e           | stimates             |

|----------------------------|-----------------------------------|-------------------|---------|------|--------------------------------|-------------------------|--------|-----------------|----------------------|------|------------------------|----------------------|

| Year of HVM<br>(20k/month) | 2024                              | 2025              | 2026    | 2027 | 2028                           | 2029                    | 2030   | 2031            | 2032                 | 2033 | 2034                   | 2035                 |

| Stack (~1.3x/1.5years)     | 3x                                | xL                | 4xxL    | 5x   | xL                             | 7xxL                    | 1x)    | αL              | *1yyyL               | *1z  | zzL                    | *2xxxL               |

| Tier                       | 2 (                               | or 3              | 3 or 4  | 3 (  | or 4                           | 3 - 5                   | 4 -    | - 6             | 5 - 7                | 6 -  | - 8                    | 7 - 10               |

| Vertical pitch [nm]        | 39                                | - 45              | 38 - 43 | 38   | - 42                           | 37 - 41                 | 36 -   | - 40            | 35 - 39              | 34 - | - 38                   | 33 - 37              |

| Memory height<br>[μm]      | 12                                | - 14              | 15 - 19 | 18   | - 27                           | 24 - 36                 | 34 -   | - 45<br>MILC/MI | 45 - 62              |      | - 74<br>roelectric —   | 70 - 84<br>Resistive |

| Charge trap (CT)           | Contin                            | nuous CT          |         |      |                                | CT isolation            |        |                 | — Мо                 |      | 'Re<br>ND <sup>3</sup> |                      |

| Channel                    | Poly Si                           | grain CIP         |         | MILC | <sup>1</sup> /MIC <sup>2</sup> | TiN/W —                 |        | -               |                      |      |                        |                      |

| WL metal                   | Wo                                | r Mo              | Мо      |      |                                | Continue                | ous CT | CT is           | olation              |      |                        |                      |

| Layout/Structure           |                                   | r array<br>onding | Bonding |      | or                             | Bonding<br>Multi Bondin |        |                 | nory holes b/w slits |      | FeNA                   | ND ReNAND            |

| Peri. CMOS                 | Poly S                            | Si Gate           |         |      |                                | HKMG                    | Verti  | cal Pitch -{    |                      |      |                        |                      |

| *Trand Extrapolation       |                                   |                   |         |      |                                |                         |        | Tier -          |                      |      |                        |                      |

<sup>\*</sup>Trend Extrapolation

Multi Bonding

Bonding

<sup>&</sup>lt;sup>1</sup> Metal induced lateral crystallization, N. Ishihara (Kioxia) et al., VLSI 2023

<sup>&</sup>lt;sup>2</sup> Metal induced crystallization

<sup>&</sup>lt;sup>3</sup> Jeehoon Han (Samsung) et al., IEDM 2023

# Raising Added-value in SPE

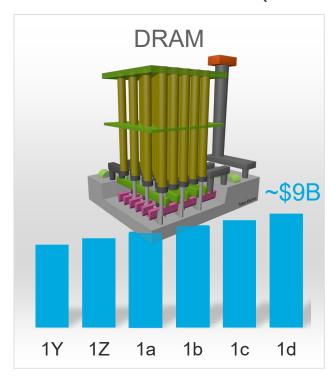

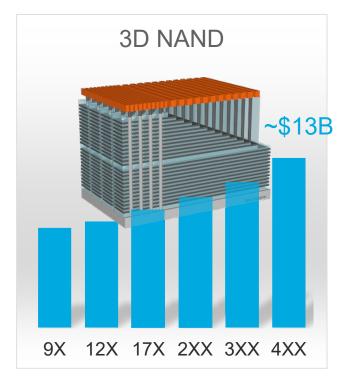

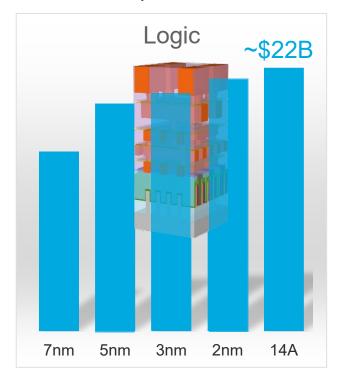

## WFE investment (100k WSPM\*, Greenfield/TEL estimates)

Expanding business opportunities for SPE manufacturers on arrival of new applications and rising level of technological difficulty

7. SPE New Equipment Initiatives

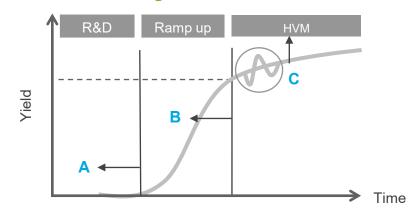

# **Development Efforts**

# Our Growth Opportunities in the Frontend Market

- CAGR driven by Al-related devices to continue to drive high growth of WFE's CAGR

- Leveraging TEL's strengths to address high-growth market areas:

- Leading-edge logic: The etch market is expected to grow by 2.7 times, the deposition market by 2.5 times\*

- DRAM: The etch market is expected to grow by 2.3 times, exceeding the CAGR of WFE\*

- By introducing new products focused on the key technological inflection points, we aim to further expand our areas of entry

\* TEL Estimates

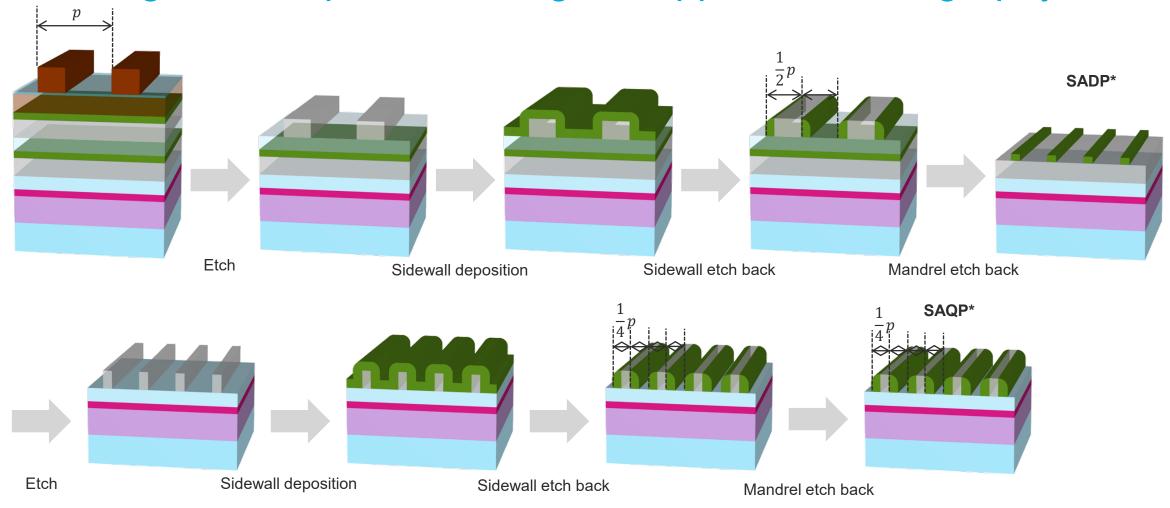

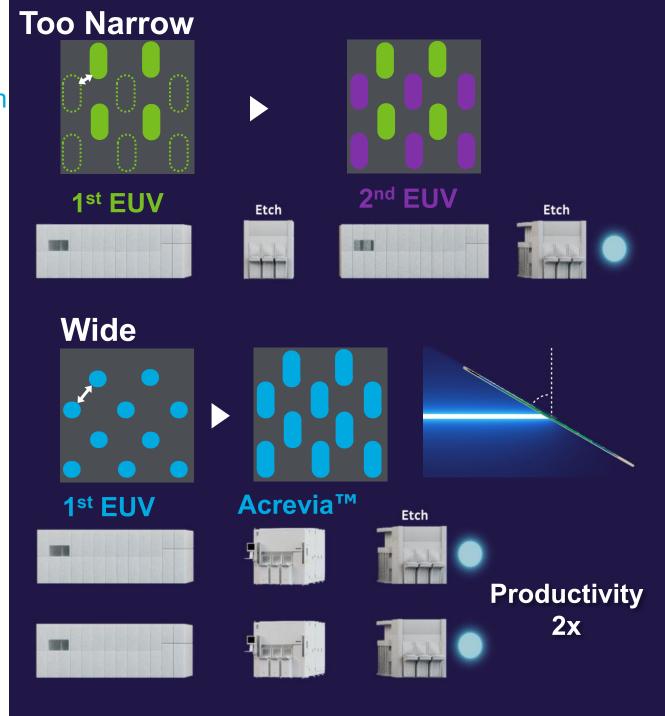

# Growth opportunities at Technological Inflection Points in Frontend Process

## Logic: GAA\*1, BSPDN\*2, CFET

- Adaption of High-NA lithography, combined with multi-patterning and MOR technologies, presents

opportunities for new technology Acrevia<sup>™</sup>

- Adoption of multi-patterning to increase demand for deposition, etch, and cleaning processes.

- GAA and CFET transistors to drive an increase in gas chemical etch processes

- New materials like ruthenium and structural innovations such as air gaps to generate fresh opportunities

## DRAM: HBM, VCT\*3, 3D DRAM

- Adoption of multi-patterning driving increased demands in deposition and etch

- Capacitor formation remains essential, driving ongoing demand for advanced etch and deposition

- 3D DRAM leading to increased processes in deposition, etch and gas chemical etch

## NAND: Beyond 4xx

- Increased layer counts leading to higher investments in deposition and etching processes

- High aspect ratio etch to become increasingly important

- New materials such as molybdenum, and low-resistance channel silicon to be utilized

7-1. Frontend, Patterning Technologies

# Self-aligned Multiple Patterning to Supplement Lithography

SADP: Self-aligned double patterning SAQP: Self-aligned quadruple patterning

TEL

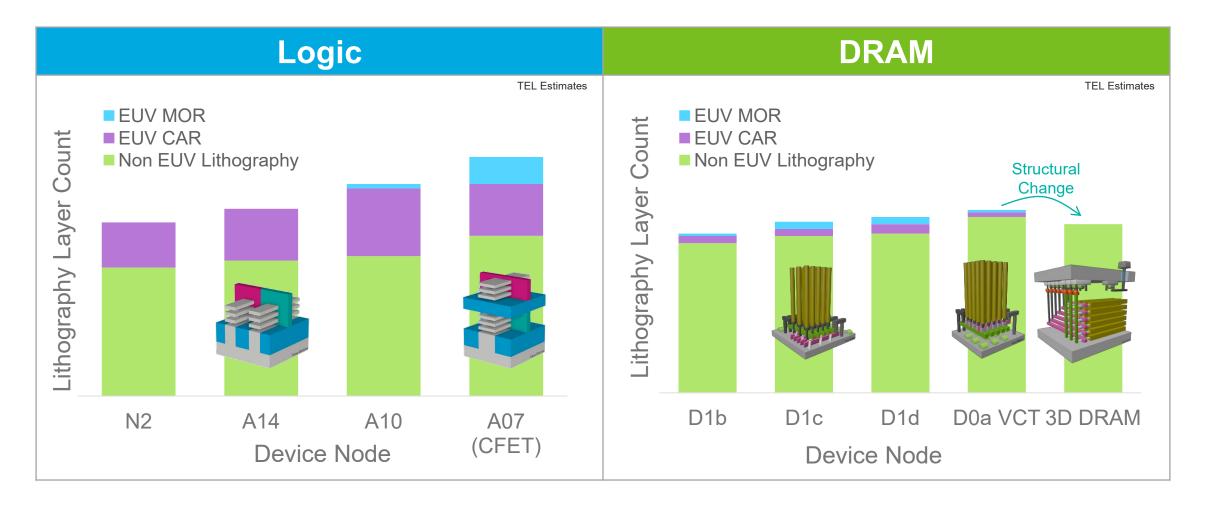

# EUV Lithography Technology Roadmap in Logic

[1] Chih-Hao Chang (TSMC) et al., IEDM 2022

[2] Shien-Yang Wu (TSMC) et al., IEDM 2022

[3] Sandy Liao (TSMC) et al., IEDM 2024

[4] Mertens and Horiguchi (imec), EDTM 2024

Source: TEL estimates

| Year of HVM<br>(20k/month)   | 2022~24 | 2025~2026               | 2027~28     | 2029~30                | 2031~32    | 2033~34                   | 2035~36                     | 2037~38                                                                                                                           |

|------------------------------|---------|-------------------------|-------------|------------------------|------------|---------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Node                         | 3nm     | 2nm/18A/16A             | 14A         | 10A                    | 7A         | 5A                        | 3A                          | 2A                                                                                                                                |

| Transistor                   | 2~1 Fin | GAA NS                  | GAA NS scal | ing GAA NS extension   | CFET       | 2 <sup>nd</sup> Gen. CFET | 3 <sup>rd</sup> Gen. CFET   | 2D material stack  IL/HK  L/HK  2D material: TMDC  MoS <sub>2</sub> , WS <sub>2</sub> , MoSe <sub>2</sub> , WSe <sub>2</sub> etc. |

| Poly Pitch [nm]              | 48~     | 45 <sup>[1]</sup>       |             | 45~42                  | 48 [3] ~42 | 45                        | ~39                         | 36                                                                                                                                |

| Min. Metal Pitch [nm]        | 23      | <b>3</b> <sup>[2]</sup> | 20          | 18                     | 17         | 16                        | 14                          | 12                                                                                                                                |

| EUV Patterning<br>Technology | Е       | UV MP, SE               |             | EUV MP, S<br>High NA S |            |                           | High NA MP, S<br>EUV MP, SE | E                                                                                                                                 |

| Resist                       |         | CAR                     |             | CAR (+MOR)             |            | CAR                       | +MOR                        |                                                                                                                                   |

MP: Multi-Patterning, SE: Single-Exposure, CAR: Chemically Amplified Resist, MOR: Metal Oxide Resist

Enhancing versatility of coater/developer to respond to future EUV lithography technologies including MOR and high-NA EUV

Investor Relations / August 4, 2025

# Coater/Developer: CLEAN TRACK™ LITHIUS Pro™ Z for EUV

LITHIUS Pro<sup>™</sup> Z released in 2012 (> 3000 systems shipped)

New features to support EUV CAR\*1/MOR\*2 to be released as on an ongoing basis

# **High Reliability**

High share in EUV market

# **High Productivity**

Maximizes output of EUV lithography tools, and reduces chemical consumption

# **High Versatility**

Supports CAR, MOR and underlayers

\*1 CAR: Chemically Amplified Resist \*2 MOR: Metal Oxide Resist

LITHIUS Pro™ Z platform with its proven mass production for various litho tools, ensures high reliability and productivity for EUV litho, along with high versatility for next-generation EUV

Investor Relations / August 4, 2025

# Outlook on Lithography Layer Count

MOR expected for Logic 10A/ DRAM D1b, development ongoing for MOR

# Example of MOR Process: The Ultimate Wet Development

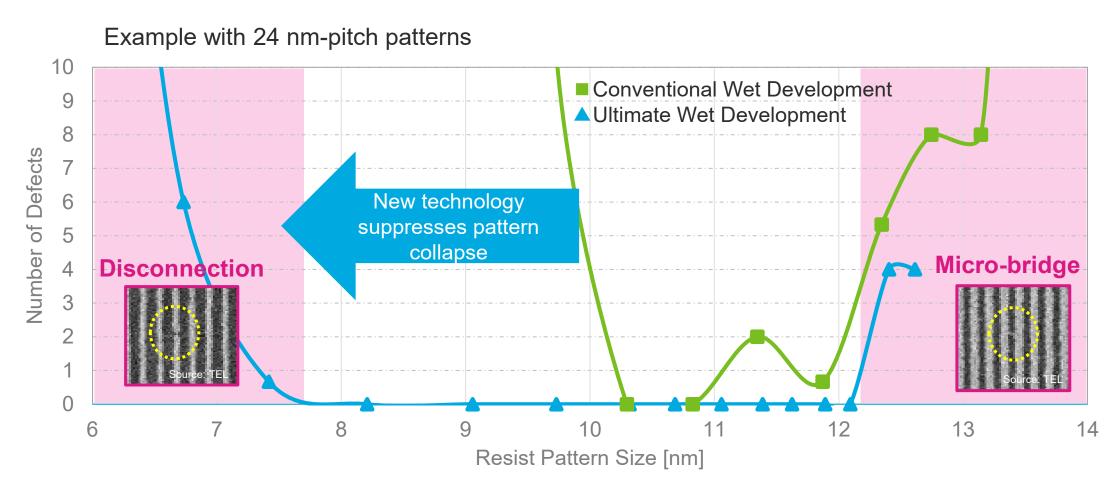

The Ultimate Development technology enables the suppression of pattern collapse

TEL

# Example of MOR Solution: The Ultimate Wet Development

\*1 Based on internal information and development targets \*2 Based on results of developing 24 nm-pitch lines

|                                     | Ultimate Wet<br>Development<br>Technology | Conventional<br>Wet Technology | Alternative Technology                                                |

|-------------------------------------|-------------------------------------------|--------------------------------|-----------------------------------------------------------------------|

| Base Technology                     | Coater/Developer                          | Coater/Developer               | Etch                                                                  |

| Process Ambient                     | Atmospheric                               | Atmospheric                    | Vacuum                                                                |

| Reaction                            | Chemicals                                 | Chemicals                      | Corrosive Gas                                                         |

| Throughput*1                        | 4x                                        | 4x                             | 1x                                                                    |

| Chemical Consumption*1              | 50% (vs. conventional)                    | 100 %                          | N/A (uses gas) exhaust processed in combustion abatement post process |

| Anti-Pattern Collapse*1 Performance | < 8 nm* <sup>2</sup>                      | > 10 nm* <sup>2</sup>          | < 8 nm*1                                                              |

| Footprint*1                         | In-Line                                   | In-line                        | Additional Footprint                                                  |

Evaluation of Ultimate Wet Development ongoing with key customers, with emphasis on productivity (throughput, footprint, maintainability, utilize existing facilities)

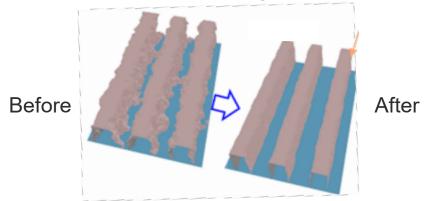

# Acrevia™

#### TEL's Original Gas Cluster Beam (GCB) System

- Beam Angle is freely Adjustable

- LSP (Location Specific Processing) Wafer Scan

- → Enable 3 Dimetional Etching

- Drastically Improve EUV productivity by EUV step reduction with fine patterning

- Realize yield by removing defect between pattern and improving LER/LWR\*

\* LER/LWR: Line Edge Roughness / Line Width Roughness

7-2. Frontend, Unit Process

# 7-2-1. Etch System

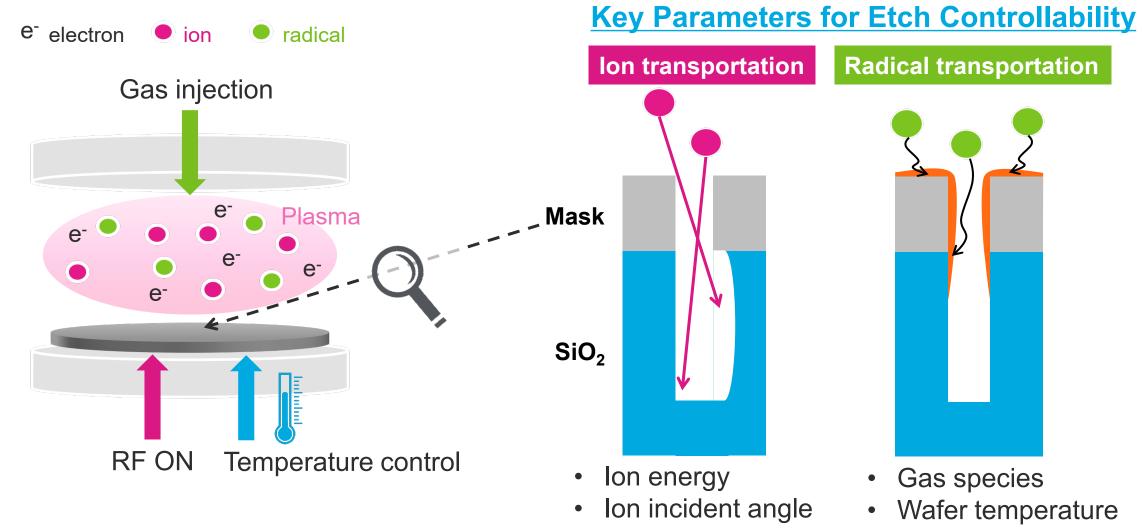

### Requirements and Various Etch Technologies

#### **Device trend**

**Technology** Required

High selectivity through precise ion control Low-damage process Profile control (vertical, etc.)

#### Scaling/new structure

Small CD\*3, high aspect ratio capacitor etch Scaled mask etch (EUV, multi patterning) HBM (increase in interconnect, etc.)

#### **Stacking**

Fast and vertical high aspect ratio etch Depth monitoring and process control Within wafer uniformity control

Etch technology with precise controllability is required for further evolution of devices

# Overview of Etching and Key Parameters

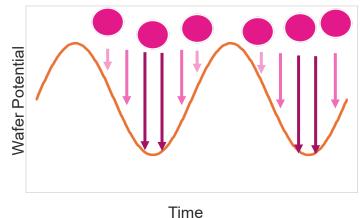

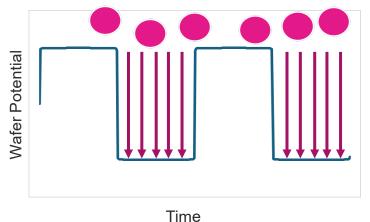

# Our Unique Technology 1: HERB™

# **lon transportation** Mask SiO<sub>2</sub>

# Conventional Technology (Sine wave)

The force attracting ions varies

→incident angle varies

(HERB™: <u>H</u>igh <u>E</u>fficiency <u>R</u>ectangular <u>B</u>ias™)

Force attracting ions are strong and consistent

→incidence angle becomes perpendicular

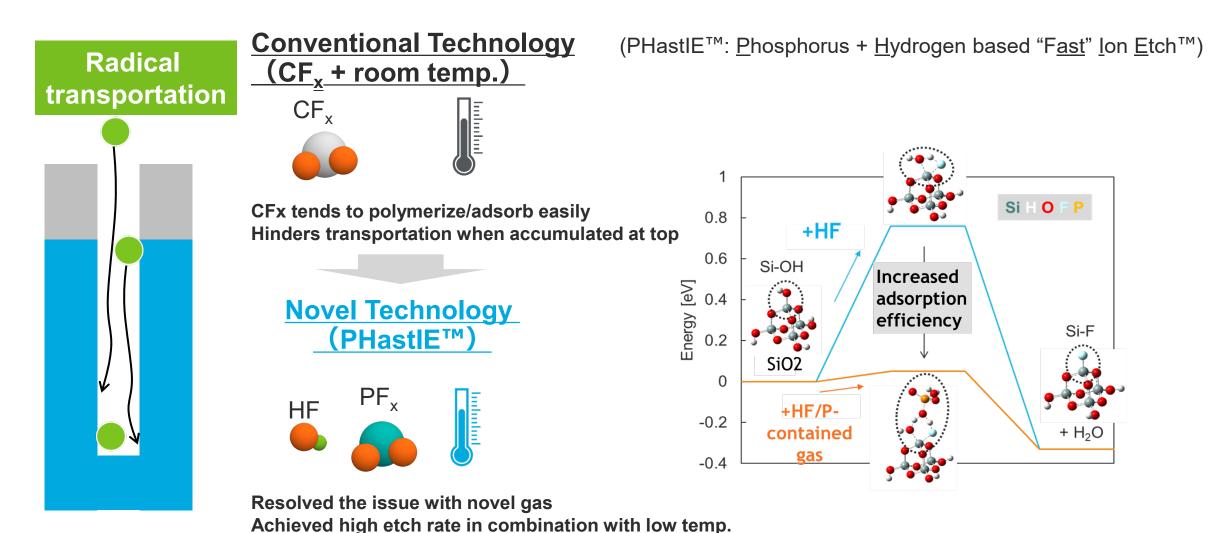

# Our Unique Technology 2: PHastIE™

# Novel Cryogenic HARC Etch

**Beyond**

**Process**

Cryogenic temp.

More Linear, Deeper & Faster

**Plasma Control**

Deep-learning Optimization

**Environment**

**Power Consumption**

Less Power

**-43**%

**-83**%

CO<sub>2</sub>e

Less Carbon Footprint

Presented world's first new cryogenic process in 2023 (@VLSI 2023), achieving both high process and environmental performance

# Future of New Etch Technologies

#### DRAM: Capacitor SiO<sub>2</sub> Etch

Investor Relations / August 4, 2025

#### **Logic: Gate Silicon Etch**

New technologies created through the development of ideal etching process development, will be applied to a variety of critical processes

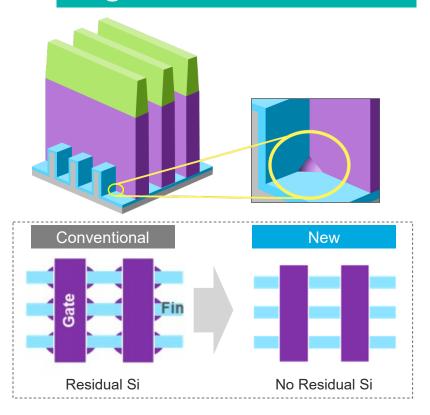

# **Business Opportunities in Logic**

Respond to changes in device manufacturing and EUV lithography for further scaling

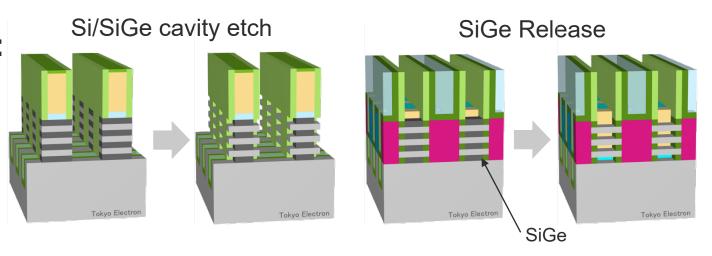

#### Initiative for GAA Nano Sheet Structures

#### Nano Sheet process challenges:

- Uniformity in rectangle shape

- Mitigation of roughness/residue on patterned surface

#### TEL's initiative: Gas chemical etch

- High etch selectivity

- High uniformity

- Residue removal/decreased roughness

Source: N. Loubet, et al., IBM, TEL Technology Center, America (IEDM2019)

Leveraging the advantages of gas chemical etch to contribute to leading-edge processes

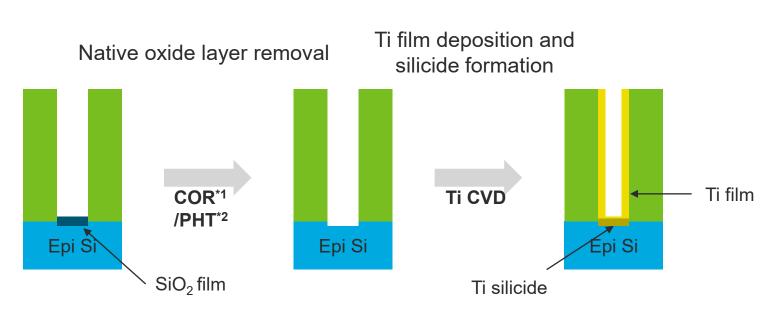

# 7-2-2. Deposition System

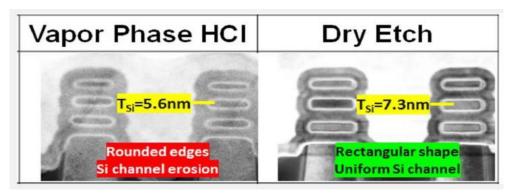

# Business Strategy in the Thin Film Deposition Market

**Expanding Market Share and SAM**\*

TEL's Market Share and SAM in Thin Film Deposition

\* SAM: Served Available Market

# Strategies in the Film Formation Business 1: Expand SAM with Single Wafer CVD

Triase<sup>+™</sup>

Episode™ 1

Episode™ 2 DMR\*

Episode™ 2 QMR\*\*

Single Reactor

Existing Platform

**Single Reactor**Equipped with up to eight process modules

\*Duo Matched Reactor

Achieved high productivity by processing 2 wfs/PM

Released in July 2024

#### \*\*Quad Matched Reactor

Equipped with a newly developed high-density plasma source

Scheduled for release in 2026

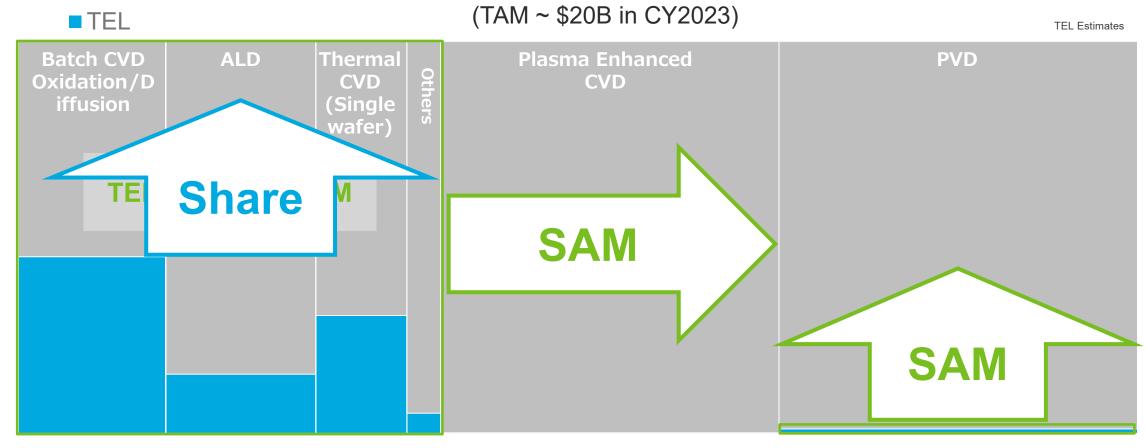

# Episode<sup>™</sup> 1: Contact Formation Process

Example of process flow

\*1 COR: Chemical Oxide Remova \*2 PHT: Post Heat Treatment

Multiple types of process modules are equipped on a high-vacuum transfer module, and low-resistance contacts are achieved by sequentially processing native oxide layer removal and metal film formation

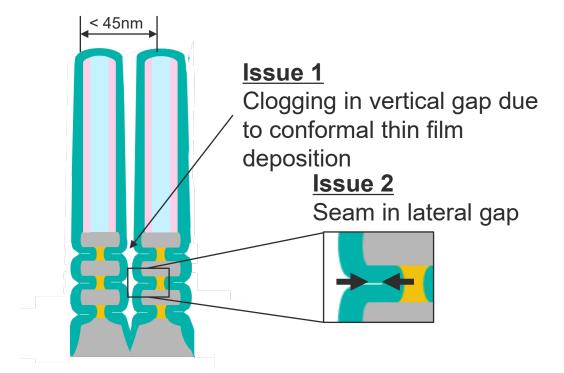

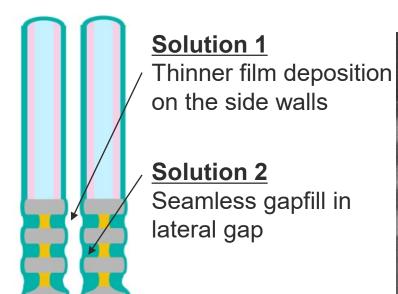

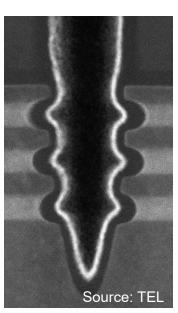

# Episode™ 1: Inner Spacer Formation - Lateral Gapfill

Issues:

Leak due to dielectric breakdown due to etching

Solutions : Improve lateral gapfill performance

Realized seamless lateral gapfill using a unique thin film deposition technique and laterally uniform film modification using a newly developed high-density plasma

Investor Relations / August 4, 2025

# Strategies in the Film Formation Business 2: SAM Expansion with PVD

#### LEXIA™ -EX Released in December 2024

- Oblique angle sputter with wafer rotation system

- Excellent thickness uniformity (1σ 0.5%)

- Unique multi-cathode\*1 configuration

- High deposition rate

- Capability of tuning film composition ratio with multiple materials

- High throughput (~100WPH)

- Significant footprint reduction vs conventional model

# Strategies in the Film Formation: Growth in Batch Thermal Process/Deposition

#### Major applications

- Silicon process in general (dummy gate, channel Si, etc.)

- Batch ALD high-k (capacitor dielectric)

- Plasma/Thermal ALD-SiN/SiO<sub>2</sub>

- Batch molybdenum (word line)

#### Development plans

- Increase load port size (8 lots, 200 wafers/batch)

- Improve exhaust conductance to mitigate pattern loading effect

- Enhance energy efficiency (elevate heater performance)

- Enhance labor reduction (one-touch start-up, self-maintenance, DX)

#### TELINDY™ PE-II

7-2-3. Cleaning System

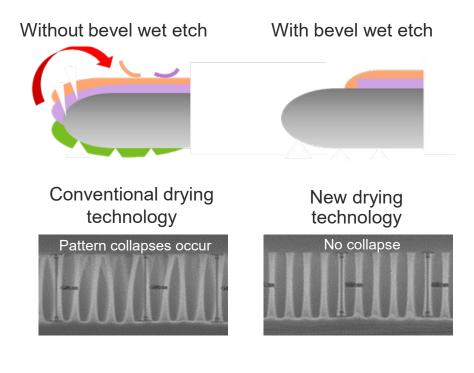

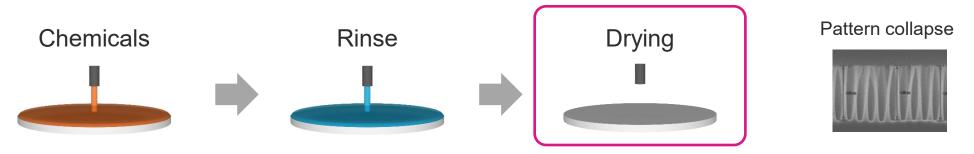

# Single Wafer Cleaning Strategy

#### Single wafer cleaning

- Bevel wet etch

- Expect annual market growth rate of around 10%

- Contribute to improving customers' yields.

Maintain a high market share by differentiating through performance in precisely removing film from the outer part of the wafer

- Prevent pattern collapse

Expand market share by TEL original technology to reduce collapse of high aspect ratio pattern

- Metal etch

Launched new dedicated SPM chambers for controlling selectivity for metal in order to solve reduced yield issues caused by dry etch damage and residue

Metal etch process

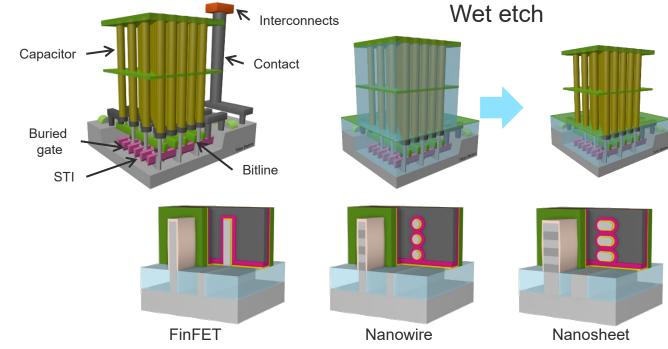

# Technology Challenges in Cleaning for State-of-the-Art Devices

- DRAM

- Post-STI etch cleaning

- Mold wet etch after capacitor electrode formation

- Logic

- Post-fin etch cleaning

- Post-nanowire/nanosheet formation cleaning

Drying technology more difficult due to further scaling and higher aspect ratios

Investor Relations / August 4, 2025

In device manufacturing

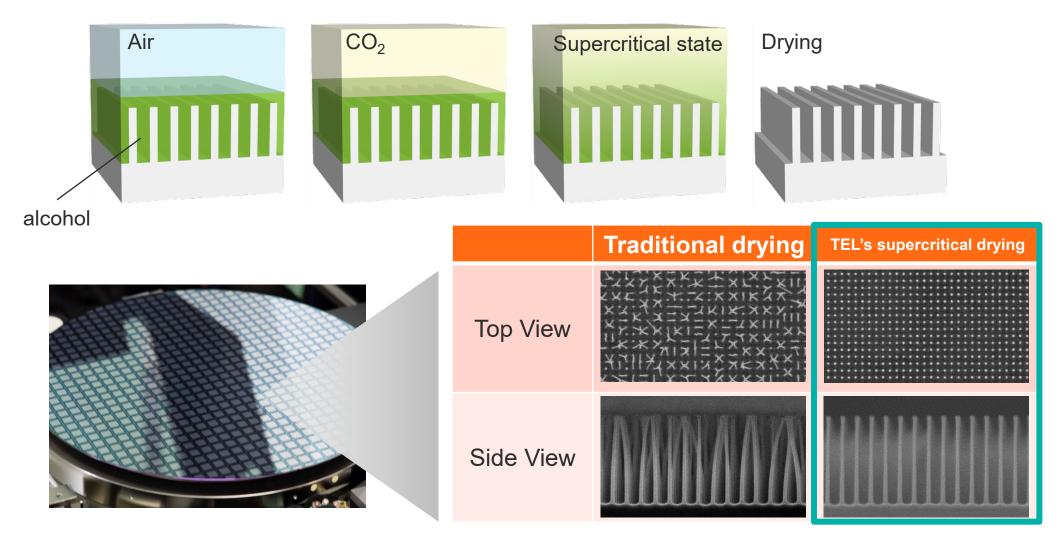

# Supercritical Drying Technology

Supercritical drying technology prevents pattern collapse

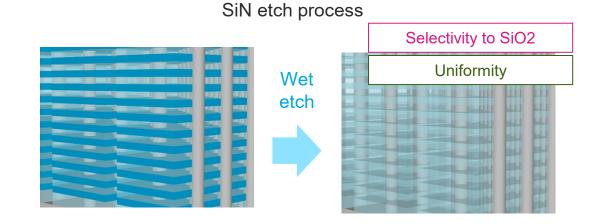

# Batch and Scrubber Cleaning Strategy

#### Batch cleaning

SiN etch and W etch processes for 3D NAND

Focus on processes that require long durations and advanced process technology. Differentiate by realizing high uniformity, high selectivity and high productivity in wet etch

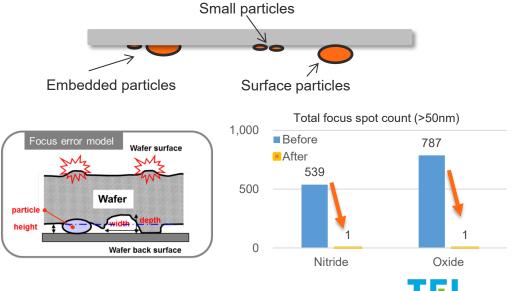

#### Scrubber cleaning

Pre-lithography process

Provide high-value solutions such as reducing particles brought in by wafers, contributing to the improvement of exposure tool availability which have grown increasingly important due to the introduction of EUV

#### Wafer back and defocus diagram

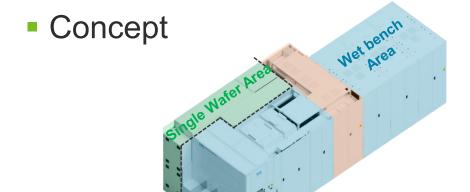

#### ZEXSTA™

A combination of wet bench + single-wafer process

| Method          | Features                                     |  |  |  |

|-----------------|----------------------------------------------|--|--|--|

| Wet<br>Bench    | High-temp/ long-duration process, wet etch   |  |  |  |

| Single<br>Wafer | Advanced drying technology, particle control |  |  |  |

- Target Application

- Advanced wet etch + advanced dry tech

- Highly selective wet etch process will be required for also 3D DRAM in addition to 3D NAND

- High throughput + surface cleanliness

High surface cleanliness is required for logic and DRAM

TEL will contribute to customer technology development by continuing to create new value, overcoming the constraints of traditional equipment classifications

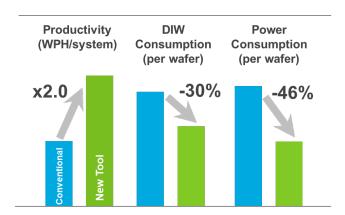

# **Development of Cleaning Systems**

# High Productivity Wet Bench (EXPEDIUS™-R)

Industry's first large-batch process (increased wafer counts)

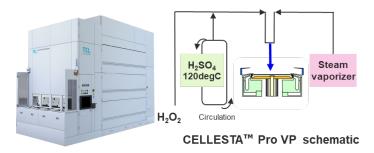

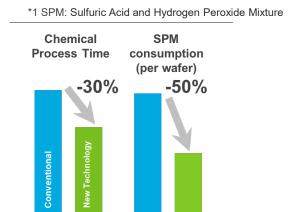

#### SPM\*1 Vapor Technology (CELLESTA™ Pro VP)

Enabled higher temperature process due to a more effective rection by adding water vapor to chemicals

# Simultaneous Scrubber (CELLESTA™ MS2)

A tool enabling AS\*2 process on wafer frontside and physical brushing process on wafer backside simultaneously in a single chamber

\*2 AS: Atomized Spray

7-3. Backend Business Strategy

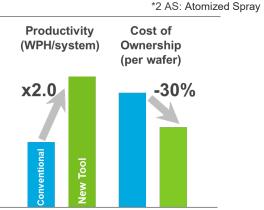

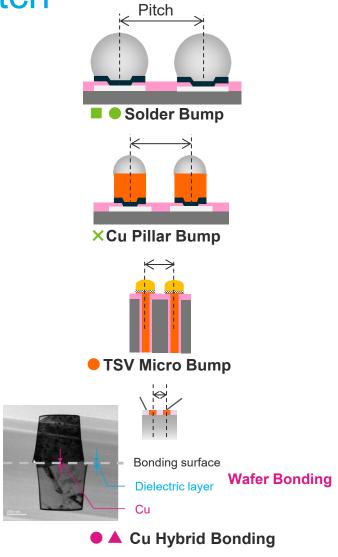

# Semiconductor Technology Node and Bump Pitch

Introduction of wafer bonding technology accelerates further reduction of pitch

Investor Relations / August 4, 2025

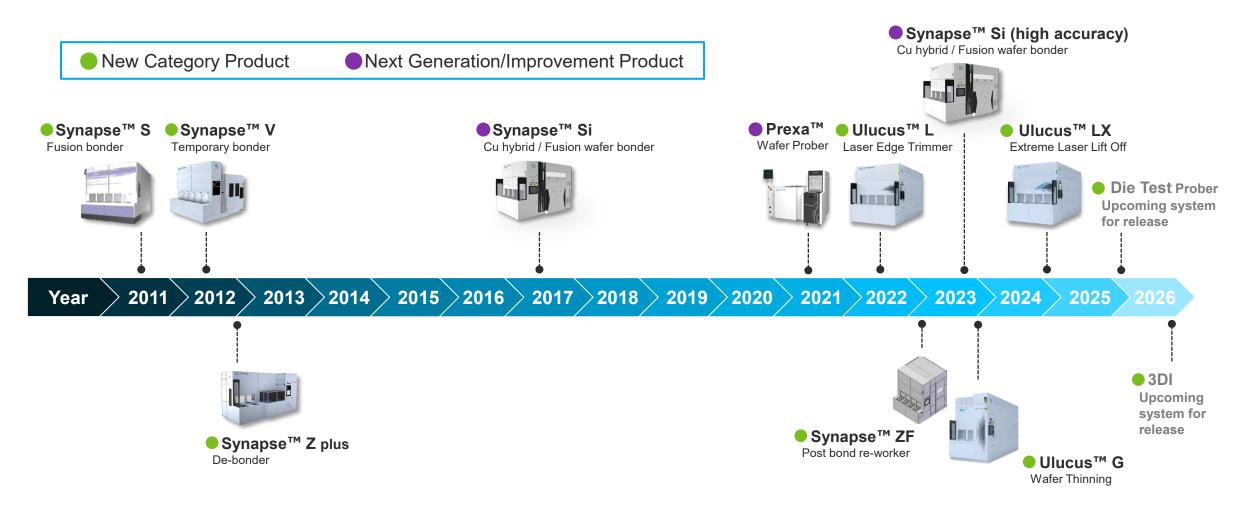

# History of Product Launches in Assembly and Test\* Systems

Accelerating product development to prepare for the era of 3D integration

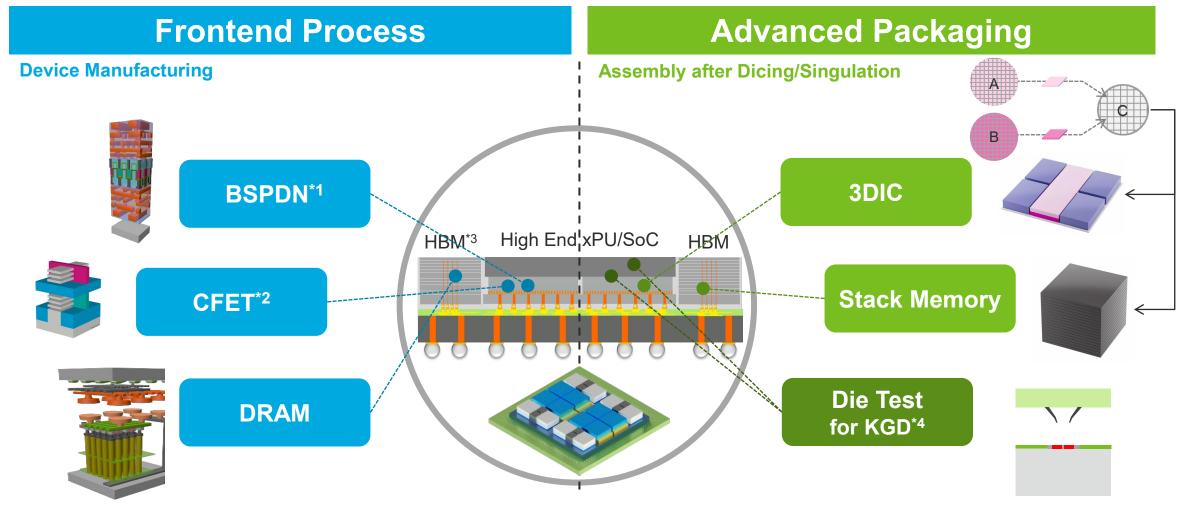

### 3DI / Test Business Expands Opportunities for HPC/AI Device

<sup>\*1</sup> BSPDN: Back Side Power Delivery Network

<sup>\*2</sup> CFET: Complementary Field Effect Transistor

<sup>\*3</sup> HBM: High Bandwidth Memory

<sup>\*4</sup> KGD: Known Good Die

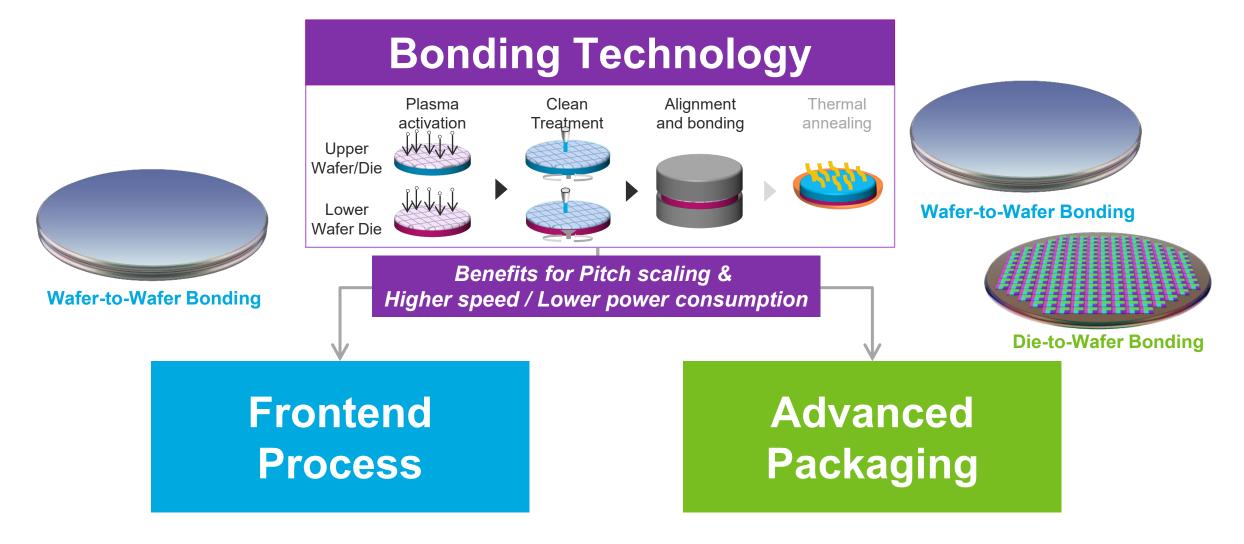

# TEL's Opportunities for Bonding Technology

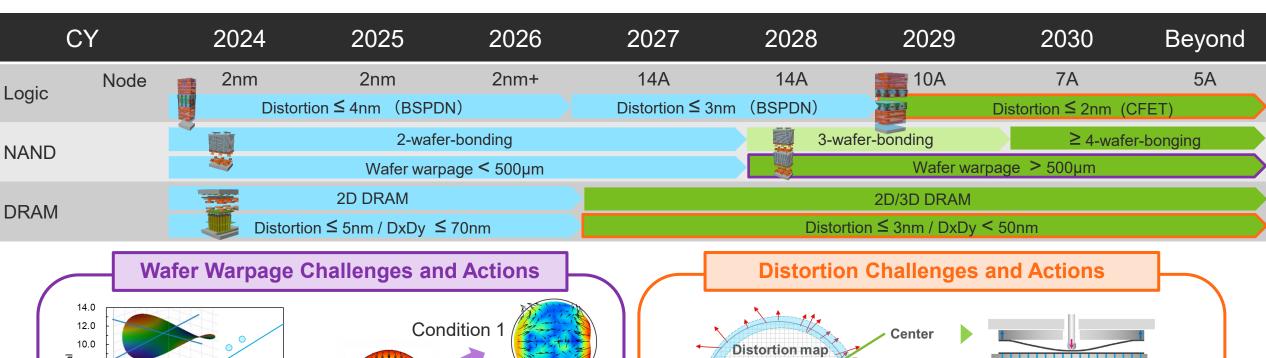

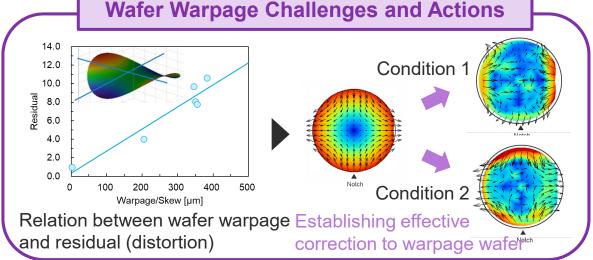

# Wafer Bonder Technology Roadmap and Challenges

TEL is developing various technologies in advance to prepare for next-generation devices

EL

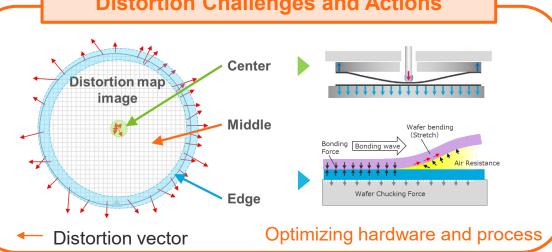

# **Bonding Process Equipment TAM\***

# Anticipating a TAM CAGR of 24% from CY2025 to CY2030

- Projected to achieve 300 billion yen by CY2030

- Encompassing both frontend processes and advanced packaging equipment

- Addressing bonding/debonding, slicing, and thinning process equipment utilizing various technologies

\* TAM: Total Available Market

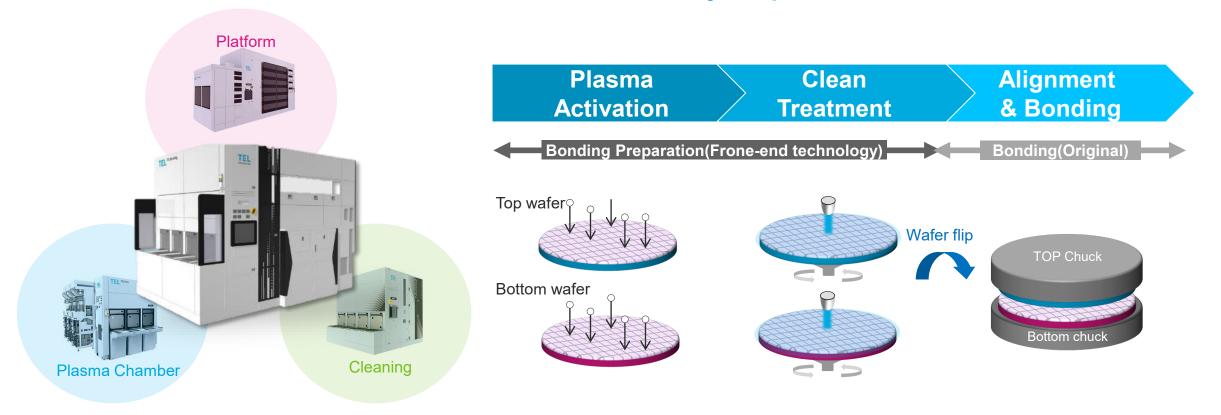

# Wafer-to-Wafer Permanent Bonder Synapse™ Si

- TEL's existing broad technology and business contributing effective product development/CIPs

- Making good progress with major memory, logic customers towards high volume manufacturing

- Leading W2W Fusion/Cu hybrid bonding technology for next generation device manufacturing

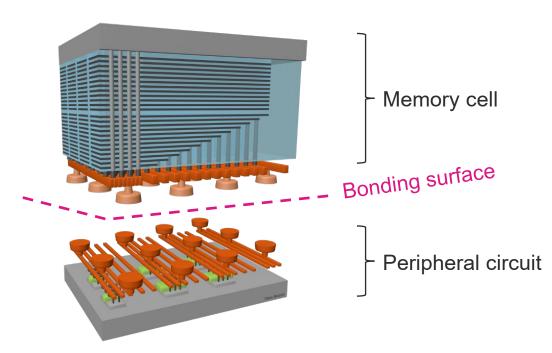

# Broad Applications and Expansion of Bonding Technology

| Application        | Frontend Process                              |                                      |      |                                                             |                                                          |  |  |

|--------------------|-----------------------------------------------|--------------------------------------|------|-------------------------------------------------------------|----------------------------------------------------------|--|--|

|                    | CIS*1                                         | NAND                                 | DRAM |                                                             | Logic                                                    |  |  |

| Stacking<br>Device | Pixel + ( Peripheral ) + Logic                | 3D NAND : + Cell + Cell + Peripheral |      | 3D DRAM Si Substrate ) + Peripheral + Cell + Si Substrate ) | BSPDN & CFET  Logic + Logic + Si Substrate  Si Substrate |  |  |

| Bonding            | Wafer to Wafer<br>(CHB <sup>*3</sup> /Fusion) | Wafer to Wafer<br>(CHB)              | i i  | Vafer to Wafer<br>CHB/Fusion)                               | Wafer to Wafer<br>(CHB/Fusion)                           |  |  |

| Structure          |                                               |                                      |      |                                                             |                                                          |  |  |

| Status             | HVM*4                                         | R&D~HVM R&D                          | R&D  | R&D                                                         | R&D~HVM R&D                                              |  |  |

The design of future devices is transitioning from single bonding to multi-bonding structures

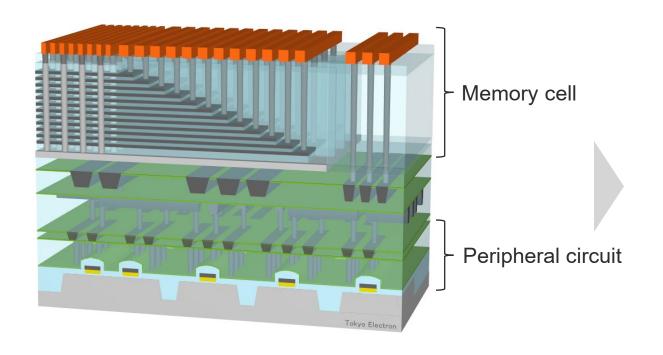

# Wafer Bonding Application for 3D NAND

#### **Current structure**

#### **New structure**

- Peripheral circuit performance deteriorates due to exposure to high temperature during memory cell manufacturing

- ✓ Long interconnects wiring

- ✓ Peripheral circuit is manufactured on the separate wafer and bond to the memory cell wafer

- higher peripheral circuit performance

- shorter TAT\* process

- ✓ Shorter interconnects wiring

# Wafer Bonding Application for Logic Backside PDN

# Broad Applications and Expansion of Bonding Technology

The opportunity for CHB/fusion bonding is growing to encompass advanced packaging

# Frontend Wafer Bonding Process and TEL Products

Integrating various TEL equipment enables next generation wafer bonding processes that deliver high performance and process efficiency

Investor Relations / August 4, 2025

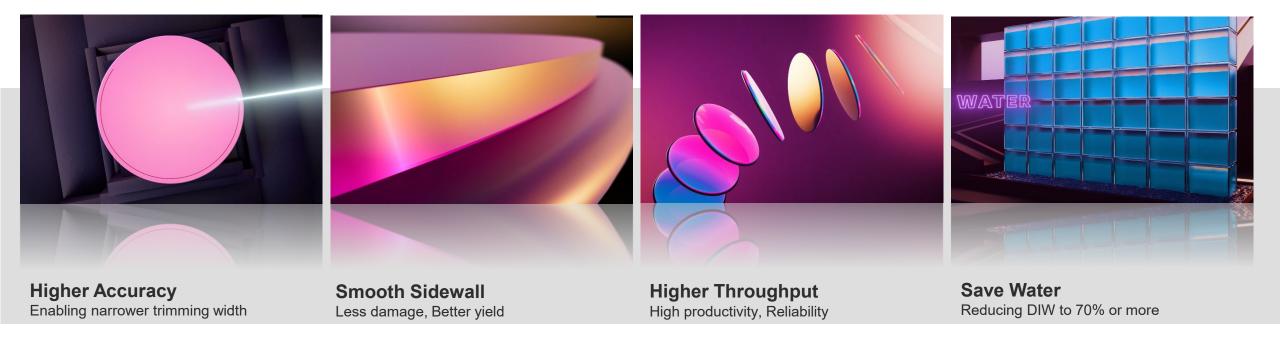

# Laser Trimming System: Ulucus™ L

#### Concept

- Edge trimming on bonded wafer

- Latest platform utilizing super clean technology from the front-end process, with the integration of laser control technology

Laser technology realizes high accuracy and quality trimming processes, and environment-friendly capability through the reduction of DIW usage

# **Laser Trimming System**

Revolutionize wafer bonding process with laser technology

Enhance yield and significantly reduce the use of DIW in the edge trimming process

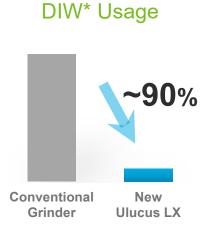

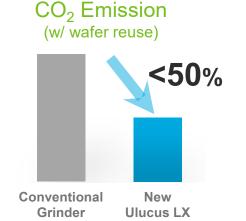

# Introducing Ulucus™ LX for Post-Wafer Bonding Process

Si wafer B

#### Extreme laser lift-off (XLO) technology

- Advanced thinning and critical technology for post-wafer bonding process

- Unique laser technology enables separation of the Si-substrate from the device layer

- Enhanced efficiency in silicon active areas

- Fewer process steps required

- Reduced need for DI water usage and CO<sub>2</sub> emission

- Opportunity for wafer reuse

- Equipment released in December 2024

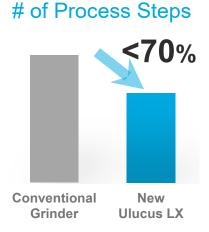

# Ulucus™ LX Advantages

#### Permanent Bonding Process with Grinding & Blade Edge Trimming (Conventional)

#### Permanent Bonding Process with XLO (Extreme Laser Lift Off)

# Active Silicon Area >1%

Conventional

Grinder

No Silicon Sludge

→ Advantage Over Grinder

Source: TEL

New

**Ulucus LX**

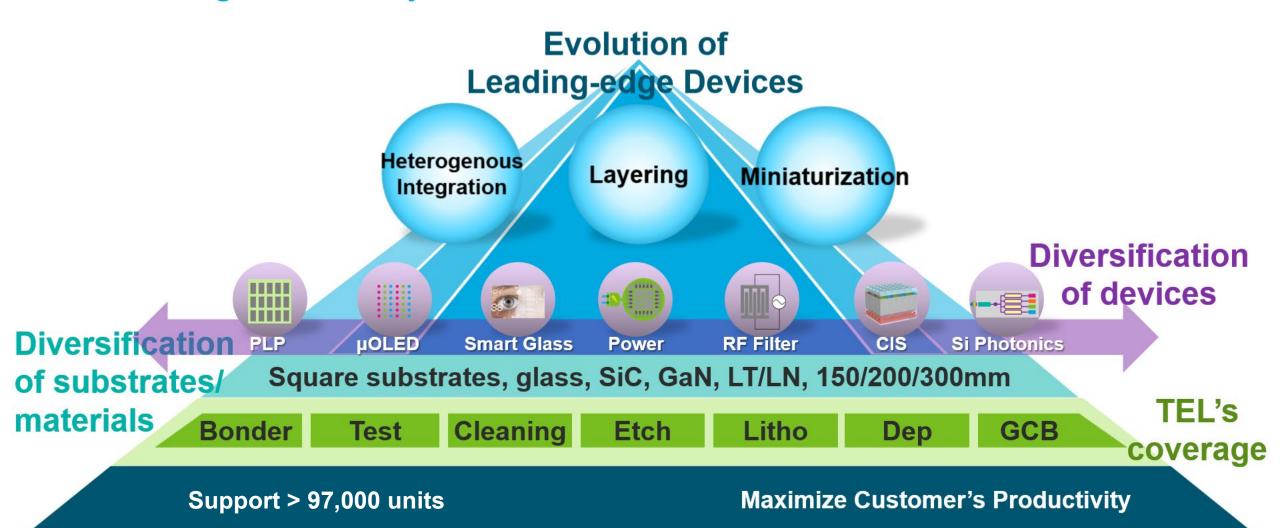

8. MAGIC Market and Field Solutions Business Initiatives

#### **MAGIC** market

- Expected market growth of 2x

(approximately \$25B in 2023, projected \$50B in 2030)

- Developing and supplying equipment for MAGIC

- Demo line ready for 200mm MAGIC

- Yamanashi, Kumamoto, Miyagi

- Massachusetts, Minnesota, Florida

# **Equipment for Mature Generations**

- Reengineered equipment for 200mm wafer

- Thermal deposition systems, coater/developer, etch systems, etc.

Sales expansions not only for replacement demand of existing customers, for emerging customers and for emerging applications

- Equipment for power devices

- Equipment for SiC wafer, 300mm etch system

- Respond to the demand for power devices, such as for representative automotive, expanding usage across various fields.

SiC epitaxial CVD system

By integrating our technological assets with new technologies, improve productivity and reduce impact on the environment

## Providing Diverse Systems and Solutions for Diverse Needs

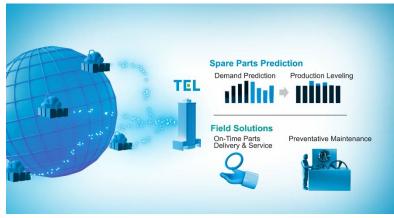

#### **Field Solutions**

# Basic Strategy for Field Solutions (FS)

- Deploying solution business based on installed base

- Development and promotion of advanced Field Solutions

- Providing leading-edge and sustainable support that utilizes the latest technology, such as DX

- Development of remote maintenance support and training tools

- Enhancing the front-lines engineers and capabilities

- Continuous skill improvement for field engineers

Support customers to maximize their business operations through services with high added value

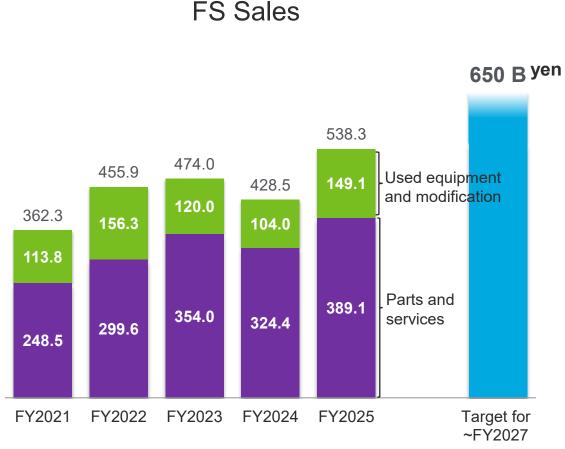

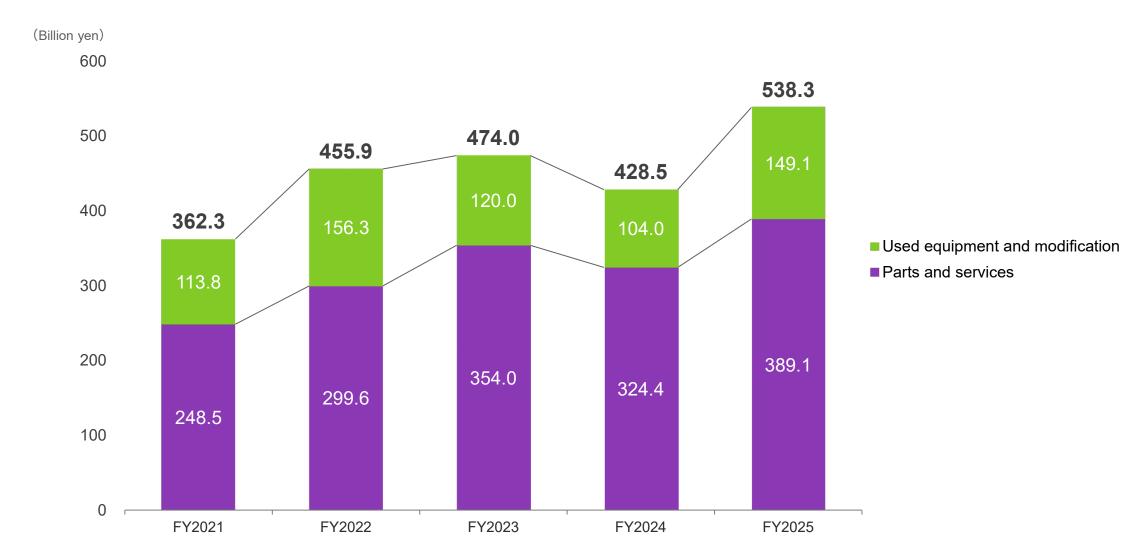

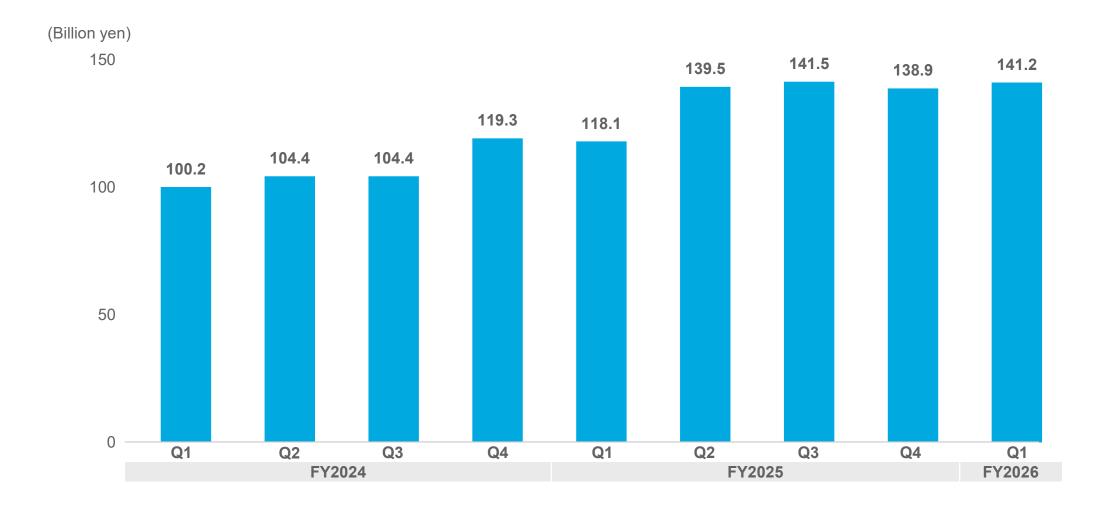

# Field Solutions (FS) Sales Results and Business Contents

#### Parts and repair

- Predictive maintenance for parts deterioration

- Appropriate parts inventory management and prompt delivery

#### Services

- Providing "comprehensive contract type" services that encompass everything from equipment delivery to after-care maintenance

- Proposing solutions that address customer demands and maximizing equipment utilization rates

#### Modification

- Productivity improvement

- Yield improvement

SAM\*1 is expanding with 97,000\*2 installed base currently and increasing by approx. 4,000 to 6,000 units each year

#### **Advanced Field Solutions**

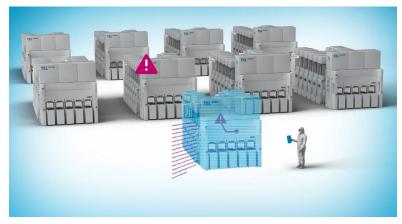

#### TELeMetrics™

- Monitoring data on individual equipment

- Knowledge management and accumulation of problem case studies

#### **Remote Support**

- Minimization of downtime through predictive maintenance of equipment

- Remote support that enables prompt response even under travel restrictions

Proposing solutions with high added value centered around "TELeMetrics™" that utilize DX

9. Digital Transformation (DX) Initiatives

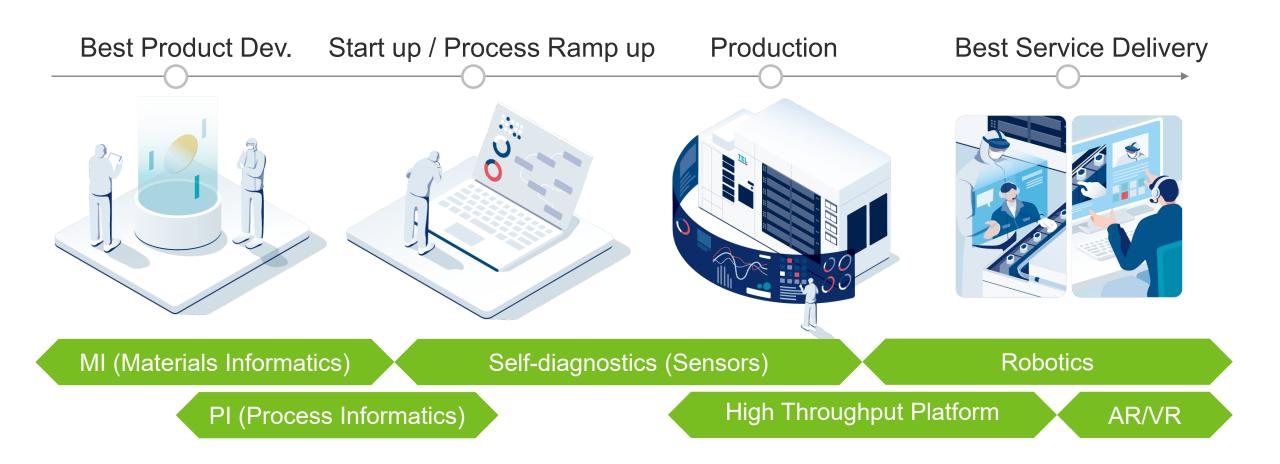

# Leveraging Digital Transformation (DX)

Developing digital enablers for use throughout the business to leverage productivity and profitability

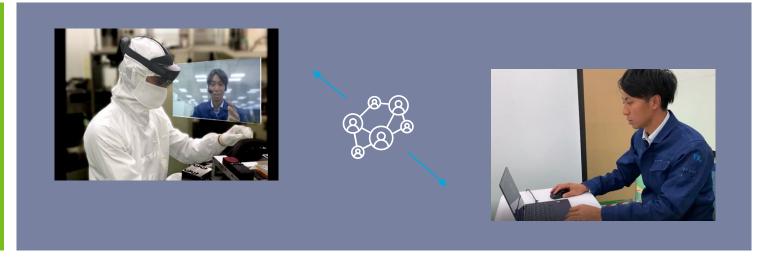

# Leveraging Digital Transformation (DX) in Field Solutions

Maximize work efficiency for startup and maintenance in the Clean Room by using smart glasses and remote expert support. Use of AR/VR and DX including digital twin technology.

Use of robots for parts replacement without human assistance is expected to minimize downtime and improve the quality of engineering work.

#### **TEL DX Vision**

The tide of DX ripples throughout the industrial world as a whole, and the semiconductor industry is no exception. It is positioned as a part of the solution toward further demands for die miniaturization and layering

Al Chip

Autonomous

Cloud Service

AR/VR

#### **TEL DX Vision**

A global company where all employees drive enterprise value creation sustainably through activities such as value addition and efficiency improvements by leveraging digital technology

DX activities are ultimately a method and an opportunity to realize sustainable creation of corporate value. We have defined the image we must achieve (our "To-Be Image") in order to realize transformation

# TEL DX Grand Design

A company filled with dreams and vitality that contributes to **TEL Vision** technological innovation in semiconductors **TEL Medium-term** Achieving the Financial Model in TEL's Medium-term Management Plan **Management Plan** Net Sales ≥ 3 trillion yen Operating Margin ≥ 35% **Product Competitiveness Customer Responsiveness** The 4 Materialities **Higher Productivity Management Foundation** A global company where all employees drive enterprise value creation sustainably through activities such as value **TEL DX Vision** addition and efficiency improvements by leveraging digital technology Innovative enhancement of materiality through DX activities that connect PLM steps **DX Application Development** Manufacturing Field **DX Business** Enhancing the Management Foundation through digitization and digital technology **Platform** Skill Consciousness DX **Data Governance Development** and Culture Infrastructure and Platform

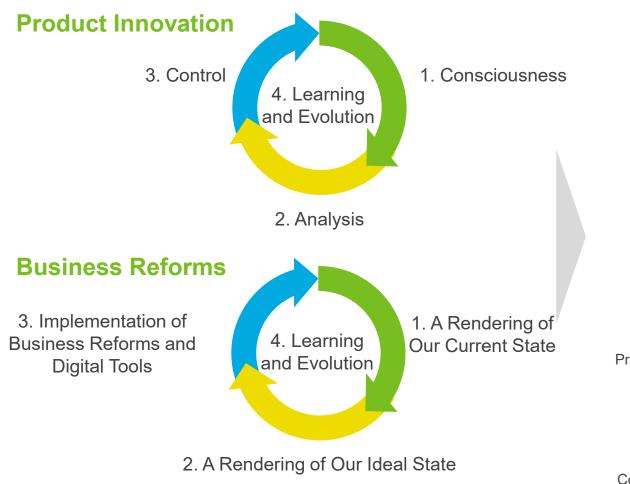

# Steps of DX Activities

#### DX in Contributing to Customers' Value Creation

#### DX in Raising Capital Efficiency

Solving issues of a higher dimension through digital transformation

# Relationships between Projects in DX-related Developments

#### **Equipment Foundation**

- Development of equipment frames

- Development of equipment foundation technologies

## Added Value Application

- Development of equipment AEPC\*

- Development of service tools

- Development related to measuring instruments

#### **DX Foundation**

- Company-wide DX training

- Data lake maintenance

- Maintenance of environments for DX development

# Capital Efficiency/ Management Foundation Application

- Development of apps for equipment

- Development of apps for the field

- Development of apps for GBP

Time

**Talents**

Through a DX foundation and DX that improves capital efficiency, we will improve the quality and speed of our work, and transition toward a use of time that creates even greater value

\*AEPC: Advanced Equipment control and Process Control, a general term for solutions and technologies that improve and optimize the performance of equipment and process control. Investor Relations / August 4, 2025

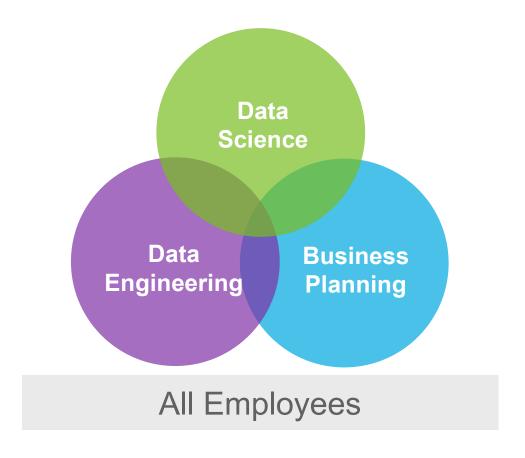

# DX Engineer Training Plan

The ability to understand and utilize knowledge of information science, such as cutting-edge information processing, artificial intelligence and statistics

The ability to realize a form of data science that meaningfully contributes to TEL's creation of corporate value, and to practice and operate data science in a manner that fits our purposes

The ability to organize issues and their backgrounds, derive solutions, and connect them to our business

Utilizing data and digital technology in our day-to-day business operations in order to optimize our business operations and create added value

Engaging in planned training to foster personnel who can capitalize data science in TEL's business

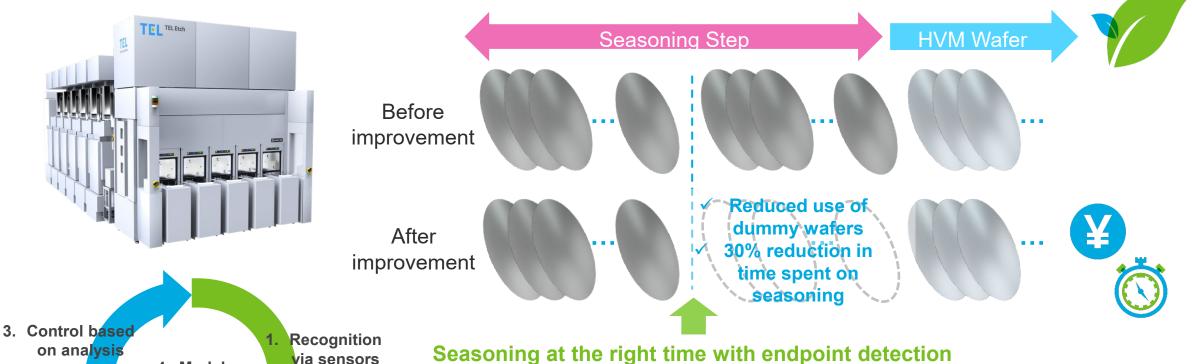

# Example Activity 1 – Increasing Productivity of Equipment:

Improving Utilization of Etch Equipment

Seasoning at the right time with endpoint detection

\*ISSM 2020, from "Seasoning Optimization by using Optical Emission Spectroscopy," published by the Company

Feedback from the sensor provided an appropriate understanding of chamber conditions and improved utilization of equipment

4. Model learning and

evolution

2. Data **Analysis**

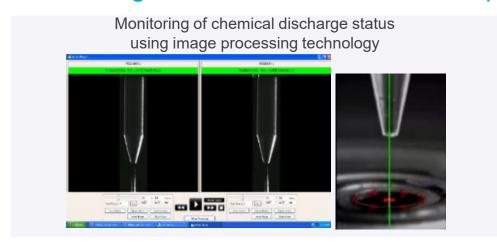

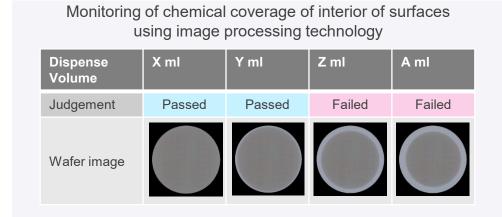

# Example Activity 2 – Increasing Operation Cost of Equipment:

Reducing Chemicals of Coater/Developer

Contributed to customer operation costs and the environment by using machine learning

TEL

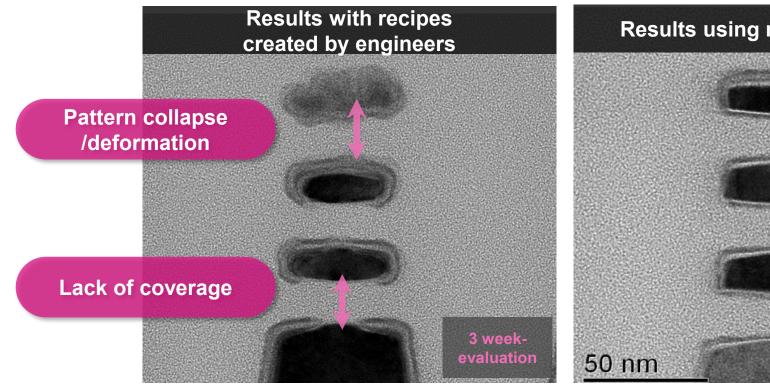

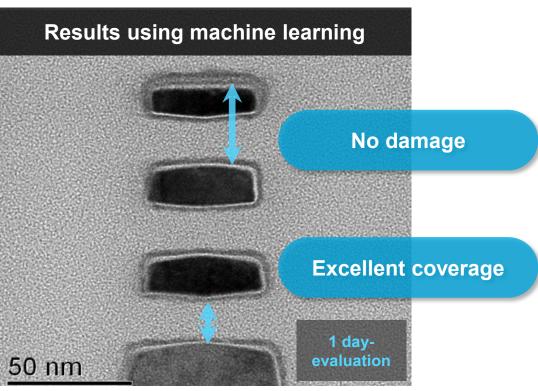

# Example Activity 3 – Increasing Productivity of R&D:

#### **Process Informatics**

Source: Tokyo Electron Technology Solutions Limited / Tokyo Electron Limited

Achieved good step coverage with no pattern deformation in the ALD process by machine learning

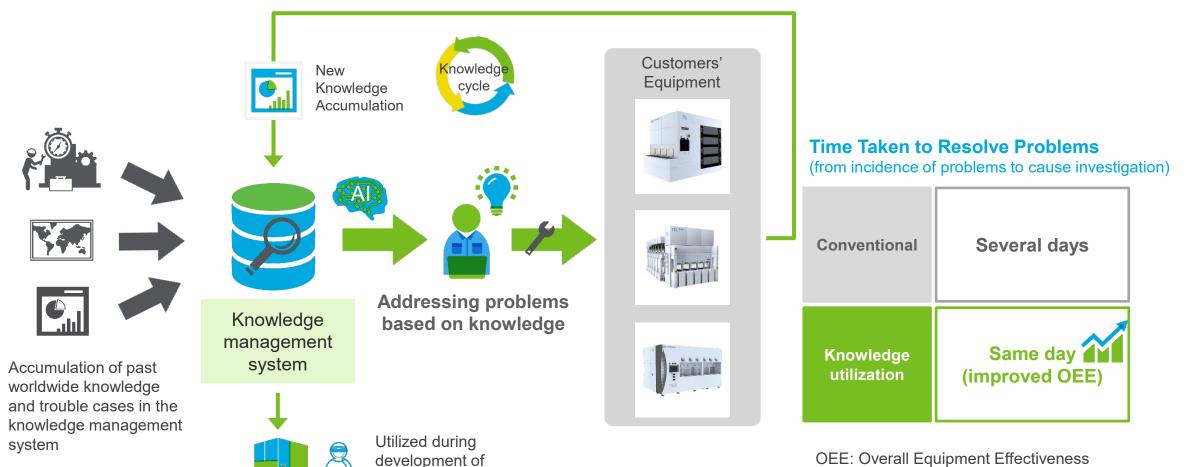

# Example Activity 4 – Improving Overall Equipment Effectiveness

OEE: Overall Equipment Effectiveness FMEA: Failure Mode and Effects Analysis

Using the Knowledge Management System to reduce the time taken to resolve problems and improve equipment operation rates

FMEA as well

Investor Relations / August 4, 2025

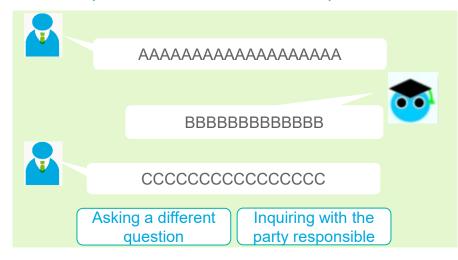

# Example Activity 5 – Increasing Productivity of Operations:

Optimizing Business Operations by Implementing Chat-bots in Back-Office Work

Responding department

- Reduce the number of inquiries, man-hours spent on inquiries

- Share know-how to resolve issue of tasks becoming too personalized, train younger employees

Legal Department, Finance Department, Personnel Department, General Affairs Department

- Make it possible to answer using choices or free input

- If chat-bot cannot provide an automated answer, make it possible to use the system to engage in inquiries

- Realize a smarter system by analyzing user histories and adding FAQs

- Make it possible to ask questions any time without hesitation

- Clarify the departments responding to inquiries

- Reduce variability in answers based on the person in charge

Reduced the number of man-hours spent by employees answering questions with introducing chat-bots in multiple departments

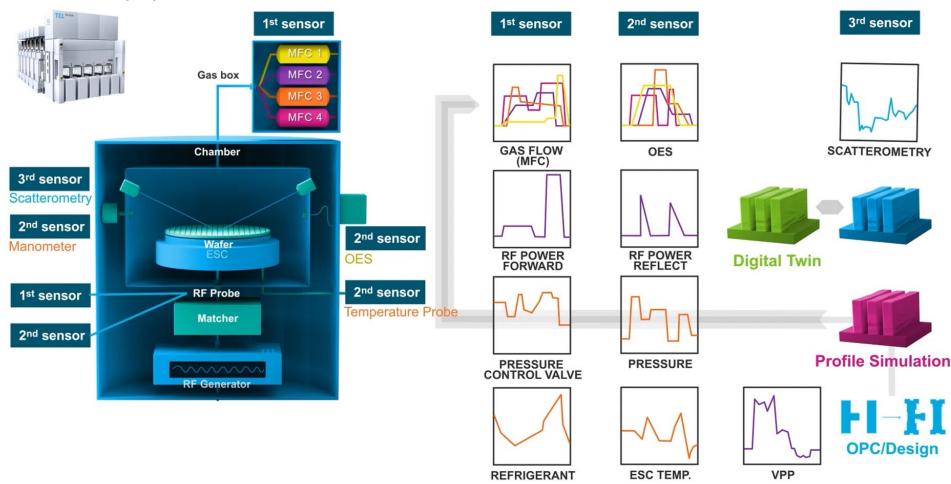

# Digital Technologies to Increase Customer Value 1:

Example in Etch Equipment

Aiming to maximize customer value using all digital technologies

## Digital Technologies to Increase Customer Value 2:

#### Example in Etch Equipment

Aiming to maximize customer value using all digital technologies

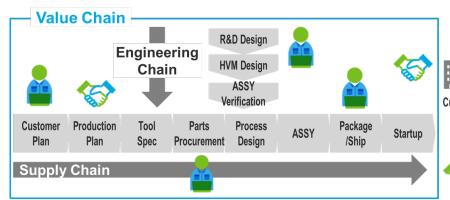

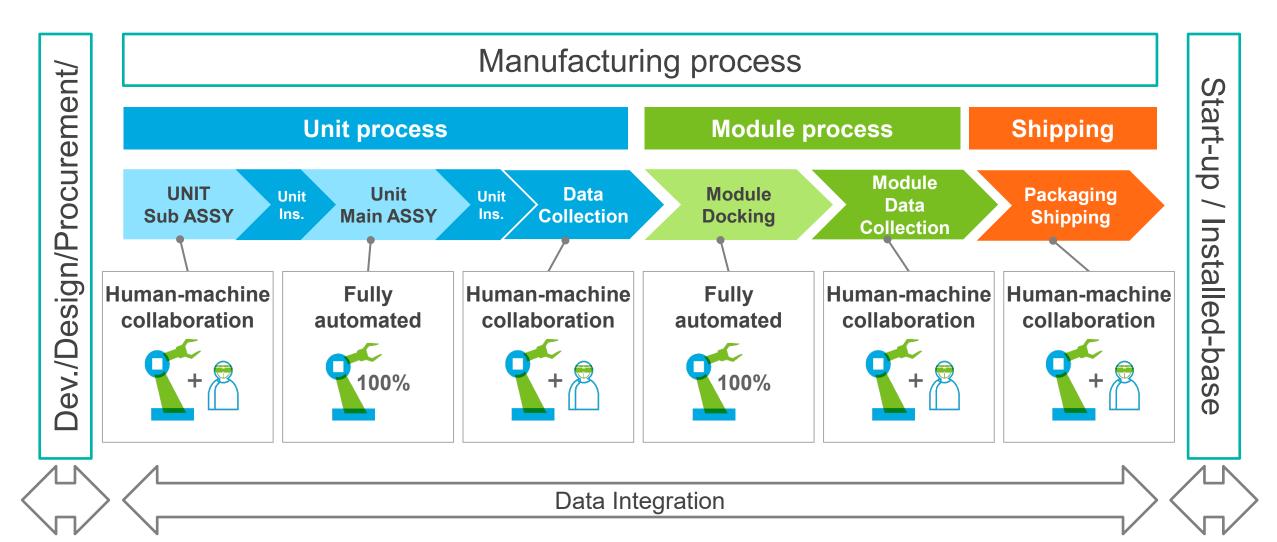

10. Procurement and Manufacturing Strategy

# Continuous Production Innovation in Pursuit of Safety, High Quality and High Reliability

- Build a production system able to quickly respond to market changes

- Shorten time from new product development to mass production

- Shorten production lead times: Achieve 100% module shipment

- Utilize DX and automation in manufacturing, and expand automated warehouse

- Significantly reduce equipment start-up time (One-touch start-up)

- Reduce start-up time up to 75% (primary target), One-touch (final target)

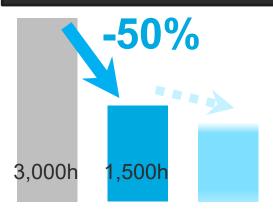

#### Shorten start-up time

Conventional → after production innovation

#### Expected outcome from shorten start-up time

- Enhance productivity and start-up quality

- Reduce accident risks

- Optimize resources and the work-life balance

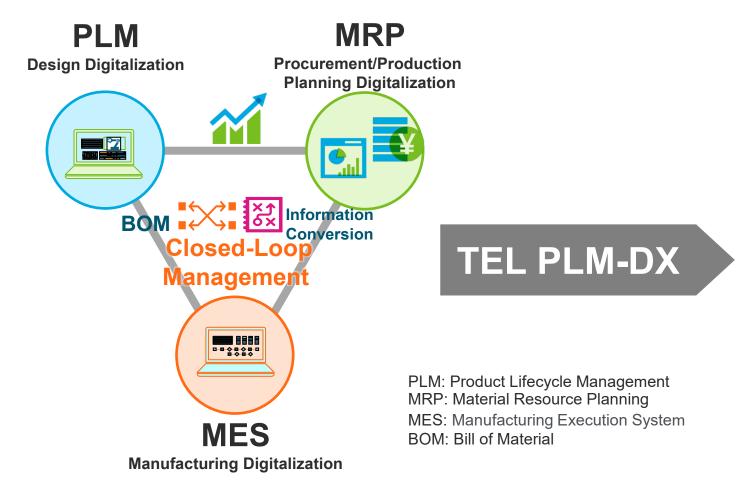

## Efforts to Utilize TEL PLM-DX and Improve Productivity and Efficiency

- Improve core system

- Production leveling < 12 months</li>

- MRP processing capability for procurement increased 10-fold

- Introduce PLM-DX and BOM concept

- Enhance production capability up to 2 times within 3 years

- Minimize manufacturing lead time

- 3-fold increase in design efficiency

- Reduce new product development period by half

"Shift Left" production plan toward the business scale of 1 trillion-yen procurement

TEL

# Build a Sustainable Supply Chain

- SUITANABLE GOALS

FRANKS STREET

AND SERVICE S

- Fair and transparent relationships and reliable trust relationship with our business partners

- Implement CSR/BCP assessments based on industry codes of conduct

- Share knowledge in such areas as safety, quality, the environment and compliance

Production trend briefings twice a year (procurement amount ratio: 90%)

Partners Day

once a year

procurement amount ratio: 65%

#### E-COMPASS

Applaud environmental impact reduction activities, adding environmentally related items to assessment studies

- ✓ Reduce CO<sub>2</sub> emissions and the amount of energy usage

- ✓ Introduce renewable energy

- ✓ Promote resource conservation

- ✓ Promote waste reduction and recycling

- ✓ Promote activities for reducing the environmental impact of logistics

#### Procurement BCP and Proactive Procurement Activities

Mid- and long-term forecast

Promote "Shift Left" procurement strategy

Build BCP system resilient to

procurement difficulty

Safety stock Inventory liquidity

Oversee whole supply chain from upstream to downstream

Visualize and grasp risks

Visualize supply chain

Supply chain responsive

to any kind of risks

(Raw materials, parts,

processing and assembly)

Strong and reliable supply chain

Risk management on business partners

Strengthen partnership

#### **Measures for procurement BCP**

#### Early procurement of parts

- Early procurement for long term

- Ensure inventory exchange flexibility among factories

- Inventory reductions in total

#### Secure semiconductor devices

- Secure semiconductor devices for our equipment

- Visualize and streamline distribution channel

- Collaborate with semiconductor makers

- = TEL can be a customer of our customers

#### Parts and Suppliers

- Identify and analyze risk parts

- Multi sourcing of producing countries

- Standardization, centralization and decentralization of parts

- Measures to secure capacity for us

# New Production Building Construction at Tokyo Electron Miyagi

- Total floor area: Approx. 88,600m² (planned; excluding the ancillary facility area)

- Structure: Steel frame structure with a base isolation system

- Number of floors: 5 above ground

- Construction cost: Approx. 104B yen

- Purpose: Manufacture of etch systems

New Production Building (Completion scheduled for summer 2027)

Realize the Smart Production concept by automating logistics functions and mechanizing manufacturing processes to provide high production capacity/quality/efficiency production lines

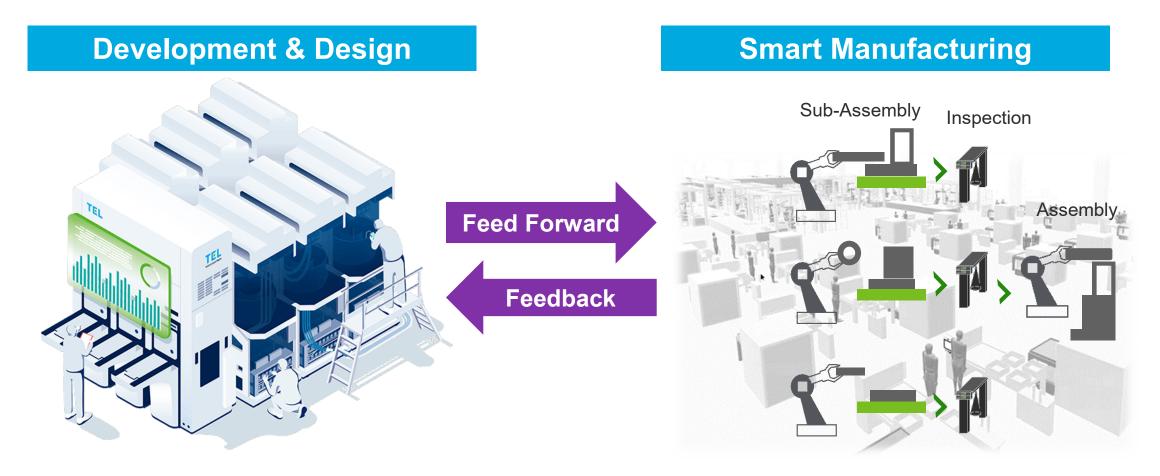

# Smart Manufacturing to Achieve High Quality and Productivity

By centralizing development and production in TEL Miyagi, we ensure continuous concurrent engineering and advanced manufacturing capabilities

#### **Vision for Smart Production**

Achieve sustainable manufacturing for the future

# Overwhelming Efficiency

through automation and standardization

# **Enhancing Adaptability**

to internal and external environmental changes

# **Product & Service Quality Improvement**

through enhanced value chain

# **Concept of Smart Production**

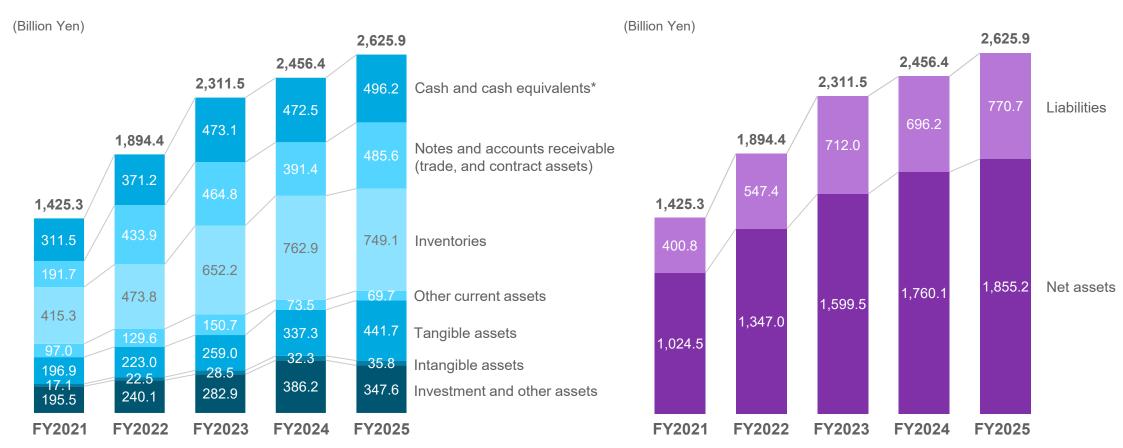

Appendix: Data Section

Yearly

## **Financial Summary**

(Billion yen)

|                                             | FY2024         | FY2025           | FY2025<br>vs<br>FY2024 | (Reference) FY2025 estimates announced on February 6, 2025 |